The IIS Chip Gallery

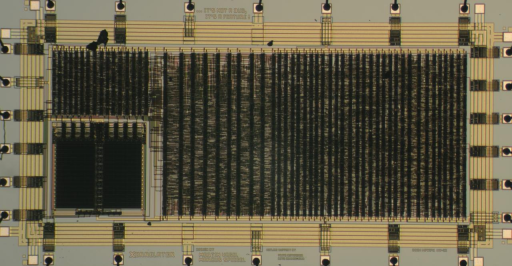

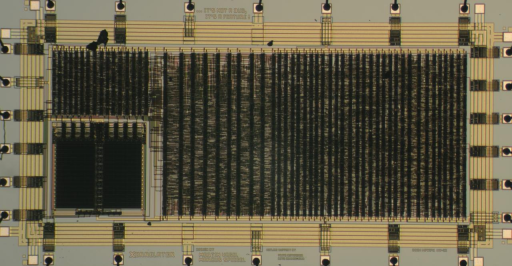

Xorrelator (1993)

by

| Application | Industrial |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Semester Thesis |

| Package | DIP24 |

| Dimensions | 3200μm x 6400μm |

| Gates | 8 kGE |

| Voltage | 5 V |

| Power | 100 mW(16 MHz, 5V) |

| Clock | 16 MHz |

Modern digital levelling meters use cross correlation techniques to improve the speed and accuracy of the measurements. The correlation is performed in two steps; a binary correlation is used for the coarse position matching, and a normalized correlation with multi-bit accuracy for the fine tuning.

The gate array solution currently used fo rthe levelling meters of Leica is too slow for their future products, since it implements a fully serial algorithm. A commercially available parallel implementation exceeds the allowed power consumption by far. The purpose of this work was therefore to develop and evaluate differemt architectures for a VLSI implementation, which met both the speed as well as the power requirements.

Using a novel parallel/serial algorithm and an on chip cache, a speed-up by a factor 5 has been reached, while reducing the power consumption at the same time by a factor of 6. Eight correlations are calculated in parallel. The ASIC has a built-in 8-bit microporcessor interface, which allows to load the measurement data and to fetch the results.

The chip has been fabricated and tested sucessfully using partial scan-path and block isolation techniques.