The IIS Chip Gallery

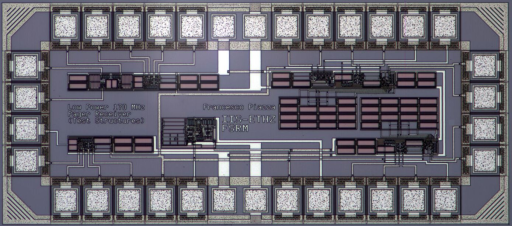

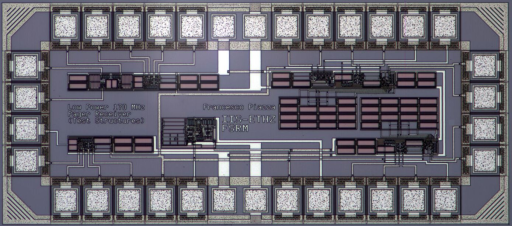

Ermes (1994)

by

| Application | Industrial |

| Technology | 1200 |

| Manufacturer | austriamicrosystems |

| Type | Research Project |

| Package | Unknown |

| Dimensions | 2240μm x 980μm |

| Voltage | 3 V |

| Power | 0.69 mW |

An RF front end for the ERMES pager has been successfully designed, manufactured and tested. The chip comprises of a low-noise amplifier with AGC, a double-balanced mixer and a varicap-tuned LC VC, and has been implemented in a 1.2um BiCMOS technology. The amplifier is a two-stage design with a linear AGC circuit. Its measured gain is 22.3dB at 170MHz, while the usable AGC range is approximately 20dB.

The mixer is of double balanced type, to achieve a good local oscillator suppression. This is needed in direct conversion receivers where a high quality IF filter is not present. Its conversion transconductance is 130uS at 170MHz. The VCO is a varicap tuned LC oscillator with external resonator. The tight phase noise reuqirement (-105dBc/Hz at 25kHz offset) dictates the use of external components, excluding a fully integrated solution. The phase noise is -74.9dBc/Hz at an offset of 2kHz from the carrier, while at 25kHz it is well below the white noise of the test system. The noise figure of the complete front-end is 6.2dB, while its power consumption is 0.69mW including biasing. This front-end is suitable for direct conversion and for superhet pager receivers.

IF components have additionallyt benn integarted on this chip: An AGC amplifier and a double-balanced mixer with integarted output filter which are scaled down versions of their RF counterparts. The measured gain of the IF amplifier is 24.3dB while that of the combination of mixer and output filter is 16.7dB. The on-chip 2-pole active filter has a -3dB bandwidth of 250kHz and does not require external parts.