The IIS Chip Gallery

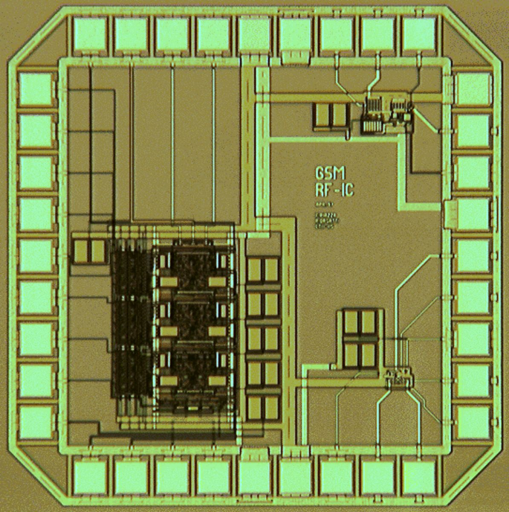

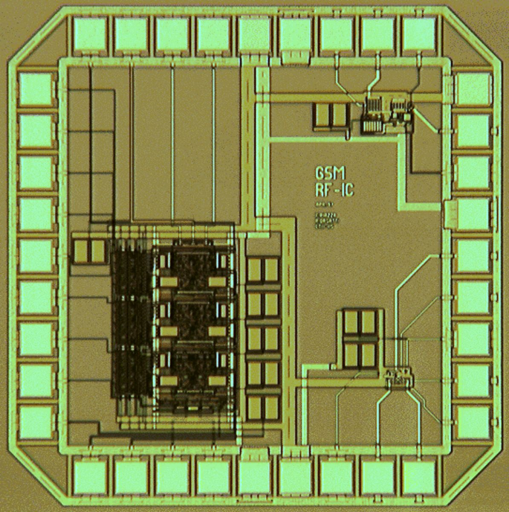

GSM_Transciever (1997)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | Toshiba |

| Type | Research |

| Package | Unknown |

| Voltage | 2.5 V |

| Power | 55 mW |

With the availability of deep-submicron technologies, CMOS has become a serious candidate for RF design. At 0.25um, the RF performance of CMOS is roughly comparable to that of a typical 1.0 um bipolar technology, but at potentially lower costs.

The aim of this project is the development of a complete RF transceiver chip for GSM applications using an analog 0.25um CMOS technology. For cost reasons, all circuits but the power amplifier must be integrated onto this chip. In order to reduce the number of filters required, a single superhet receiver with 71 MHz IF has been chosen for the receiver part. The front-end consists of a 1.7 dB NF LNA with 15 dB gain, and a double-balanced mixer with 10 dB gain. The IF amplifier is a 3-stage fully differential design with programmable gain from -20 to 60 dB in 2 dB steps. A demodulator with 4th order output filters completes the receiver. The transmitter part consists of a direct up-conversion modulator and a 2 mW preamplifier. A careful layout has been designed to prevent parasitic coupling causing instabilities in high-gain, highfrequency amplifiers. On-chip decoupling capacitors have been used extensively.

The prototype chip shown contains the LNA, the mixer (single-balanced) and the 71 MHz IF amplifier. A performance comparable to typical bipolar implementations has been demonstrated, while the total current consumption is about 22 mA at 2.5 V.