The IIS Chip Gallery

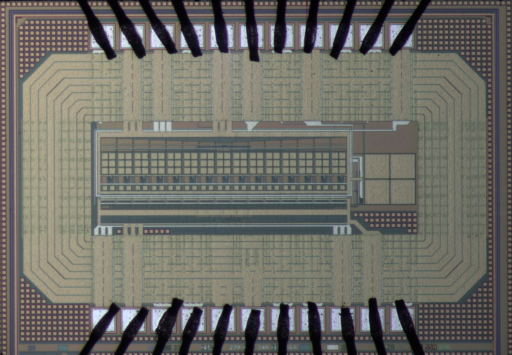

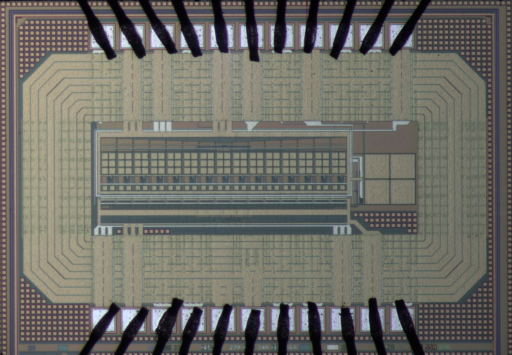

Converter (1999)

by

In modern communication devices, fast and accurate A/D converters with low power consumption are often needed. Sigma Delta converters are a very well suited solution for such applications. The traditional approach using a 1-bit quantizer, however, requires high oversampling rates for sufficient resolution. Using a multibit quantizer, the same number of bits can be achieved with lower oversampling rates, opening the way to higher signal bandwidths.

In this work, a 4-bit quantizer based on a pure flash architecture has been implemented. Its very low latency makes it suitable for inclusion in a complete Sigma Delta converter. The main goal was to achieve the given specifications of 4-bit resolution and 100 Msamples/s at very low power consumption.

The chip is implemented in a state-of-the-art 0.25 um CMOS process. Measurements showed that the circuit fulfills the given specifications at a total power consumption of roughly 10 mW, a large part of which stems from the clock network and the multi-phase clock generators. The relative contribution of these components, however, is expected to decrease in a complete Sigma Delta converter.