The IIS Chip Gallery

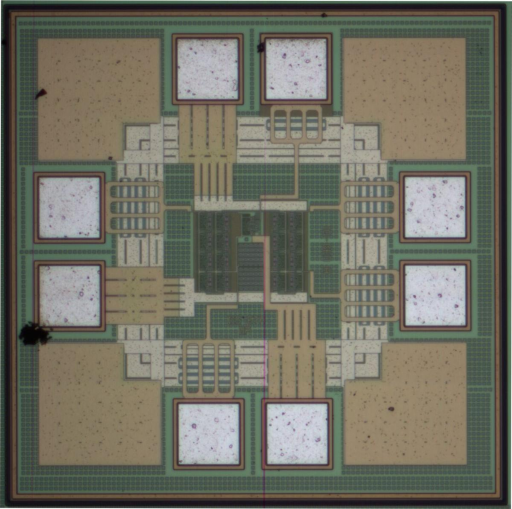

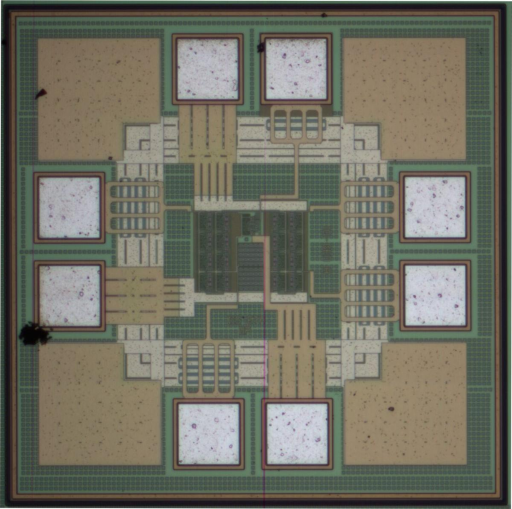

IQGenA (1999)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | STM |

| Type | Research |

| Package | Baredie |

| Dimensions | 550μm x 550μm |

| Voltage | 2.5 V |

| Power | 5 mW |

Direct-conversion receivers are an attractive alternative compared to superheterodyne receivers. They are more suitable for monolithic integration since less external components are required. But various obstacles in the design of direct conversion receivers need to be overcome, both in the front end and the baseband circuits.

Concerning the RF frontend, one of the problems is the generation of quadrature outputs of the local oscillator. Phase mismatch between these outputs must be in the range of a few degrees.

Local oscillator quadrature outputs can be generated by a passive phase shifter network. Earlier studies showed that this approach is too power-consuming. A different but simple approach to generate quadrature periodic signals is to use a divider flip-flop which is fed by an oscillator with doubled frequency. A test chip has been designed and integrated in a quarter-micron CMOS technology. The IC contains the divider flip-flop providing the quadrature signals and two down-conversion mixers. The measured mismatch of the quadrature outputs is less than 3 degrees with an input frequency up to 8 GHz. The divider\u2019s current consumption is 2 mA for a 4 GHz input signal.

One of two similar chips see also IQgenB.