The IIS Chip Gallery

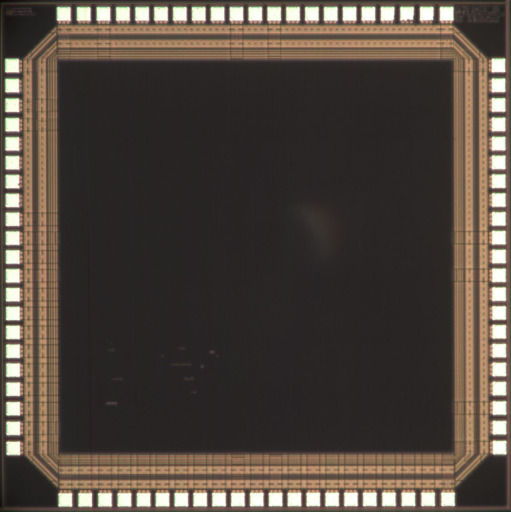

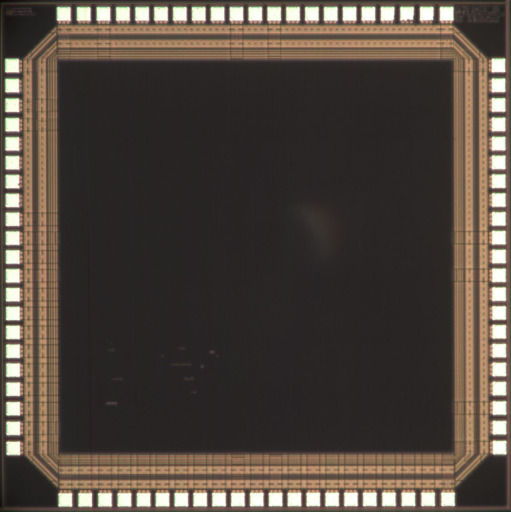

Flavio_Test (2003)

by

| Application | Low-power |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 1600 |

| Voltage | 2.5 V |

| Power | 20 mW 2.5V 100MHz |

| Clock | 100 MHz |

After having concentrated on reducing the area occupation and increasing the speed of ICs for decades, now, besides the old concerns, new issues arise. Power consumption has become a major challenge, above all in the world of portable applications, which includes a constantly growing fraction of digital signal processing, hence demanding especially for area and energy efficiency. The correct estimation of the power consumption in ICs represents therefore a crucial point to trade speed for power, keeping in mind area occupation, during the design of VLSI chips. Yet, this appears as a quite challenging issue due to the complexity of both modern digital circuits and the involved physical mechanisms of dissipation.

Within this framework, the capability of industrial CAD tools to estimate the power consumption of ICs has been studied. On this purpose, a complete power analysis flow has been lined up together with a full re-characterization of the standard cell library, starting from transistor-level simulations. On the other hand, a proper measurement set-up has been arranged. Direct evaluation on silicon has confirmed the excellent accuracy of the proposed methodology, with estimation vs. measurement agreements in the order of 10% to 20%.