The IIS Chip Gallery

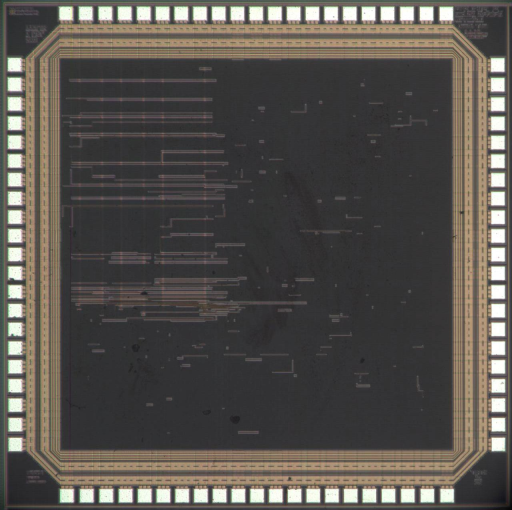

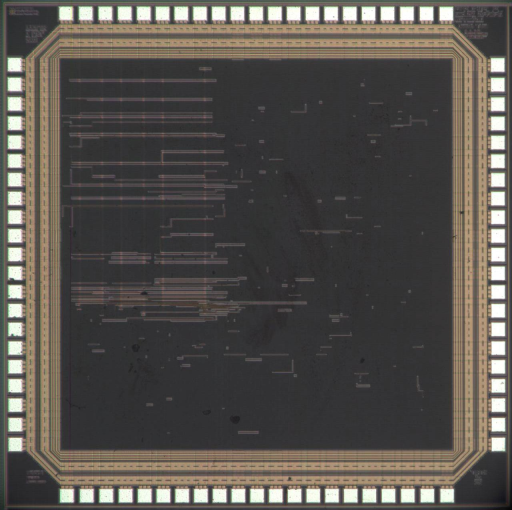

Lucifer (2003)

by

| Application | Industrial |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 30 kGE |

| Voltage | 2.5 V |

The goal of this student project was to implement an IEEE1394 compliant FireWire Link Layer Controller (LLC). The ASIC supports asynchronous transfers of up to 400Mbps and can be connected to any commercial IEEE1394 physical layer device (PHY). Receive and transmit data paths are strictly separated. The receiver block accepts data from the bus, reassembles the 32-bit words and performs a Cyclic Redundancy Check (CRC). Packets are then transferred to the 1kByte receive FIFO, where a controller can access the data via an asynchronous host interface. An additional 1kByte FIFO is located in the transmission path. The memory management of the FIFOs allows efficient communication with the host controller. Transmit operations include generation of arbitration requests and CRC calculation.

An important task of the LLC is the generation and evaluation of acknowledge packets. Missing acknowledge responses or erroneous packet formats are detected and reported. A set of control and status registers (CSR) allows configuration and control through the host interface. The CSR accepts commands for the PHY, which are transmitted as a special PHY configuration packet.

A verification environment was developed for automatic traffic generation and analysis. The chip is fabricated in a 0.25um CMOS process on 5.8mm2 chip die area.