The IIS Chip Gallery

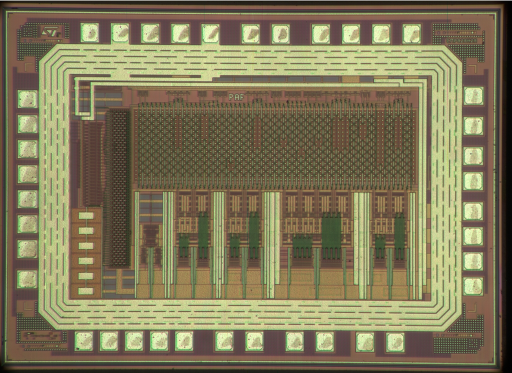

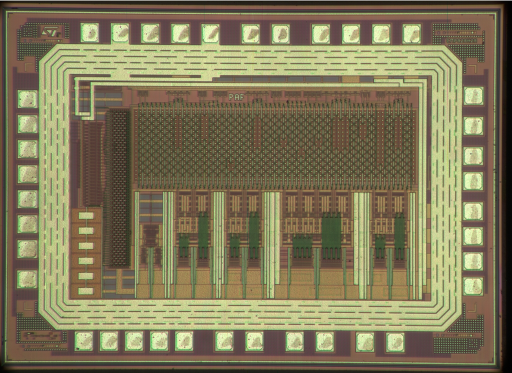

Reconstruction_DAC (2003)

by

| Application | Converter |

| Technology | 180 |

| Manufacturer | STM |

| Type | Research Project |

| Package | LCC44 |

| Voltage | 1.8 V |

| Power | 55 mW |

| Clock | 35.328 MHz |

The demand for high data rate communication systems has pushed the linearity requirements of A/D and D/A converters in a range where it is necessary to use special design techniques and architectures. Only in this way it is possible to exceed the raw limit of the present CMOS technologies that is in the range of 10 bits.

A converters using single-bit Sigma Delta modulators are well appreciated architectures that offer excellent linearity performances due to the inherent linearity of the two level quantizer at the modulator output. The semidigital filter is then an elegant way to preserve this linearity while attenuating the out-of-band quantization noise. At low oversampling ratios, nevertheless, very high signal-to-noise ratios cannot be achieved without multi-bit quantizers.

The D/A converter developed in this project uses a cascaded Sigma Delta modulator with a dual truncation architecture in which the advantages of a semi-digital reconstruction filtering are combined with the necessity of using multi-bit modulators.