The IIS Chip Gallery

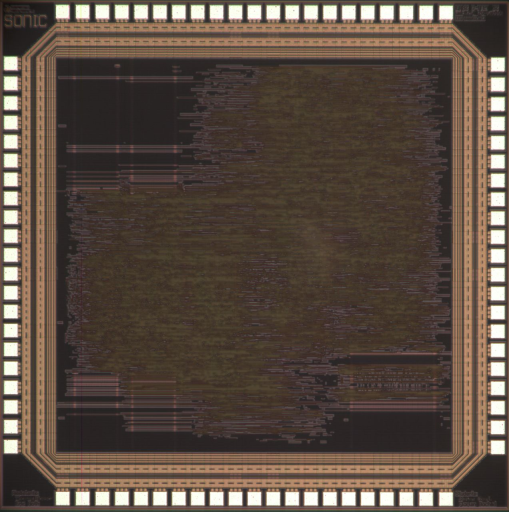

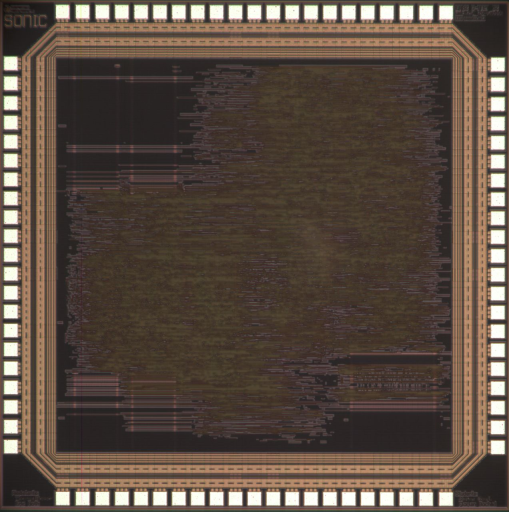

Sonic (2003)

by

| Application | Processor |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 120 kGE |

| Voltage | 2.5 V |

| Clock | 78 MHz |

The goal of this project was the development of a Reconfigurable Instruction Set Processor (RISP) for networked Consumer Electronic (CE) devices. It is optimized for audio compression, signal processing, and different cryptographic algorithms.

A General-Purpose Processor (GPP) has been extended with a Reconfigurable Functional Unit (RFU) to improve the GPP's processing performance. Application-specific operations can be defined in the RFU to extend the processor?s general-purpose instruction set. When the GPP decodes a RFU instruction, a corresponding command and two operands are sent to the RFU, where a single operation or an autonomous micro-program execution is started. Afterwards, the result is sent back to the GPP?s register file. The RFU consists of multiple arithmetic blocks, embedded memories, address generators, and a register file. Furthermore, a programmable bit operation block has been implemented to enhance the system?s performance for cryptographic algorithms. All components are interconnected by a non-blocking, programmable network. The processor has been integrated with two tightly coupled data and instruction memories on a 2.4x2.4mm2 chip die using a 0.25um CMOS technology. The processor runs at a clock frequency of 78MHz.