The IIS Chip Gallery

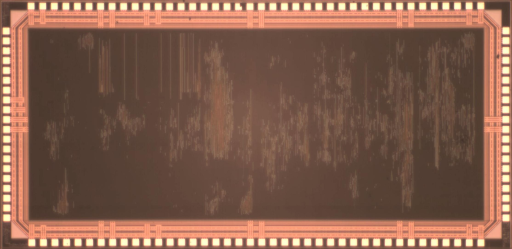

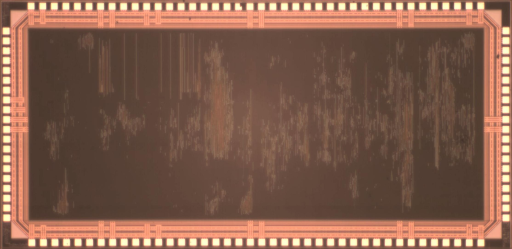

Splat_accelerator (2007)

by

| Application | Graphics |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Master Thesis |

| Package | PGA120 |

| Dimensions | 5000μm x 2500μm |

| Voltage | 1.8 V |

| Power | 300 mW |

| Clock | 147 MHz |

In recent years, the complexity of computer graphics, measured in the number of displayed polygons, has significantly increased. This trend has led to an ever increasing ratio of polygons to screen pixels. As a result, tiny triangles often fall between sampling points and get lost during rasterization, thus causing unwanted aliasing artifacts. Therefore, triangles may not be the optimal rendering primitive in all cases. Elliptical weighted-average (EWA) surface splatting addresses the issue of highquality rendering of point samples as an alternative to triangle based rendering.

In this project, the first ASIC for preprocessing of EWA splats - including transformation from object to camera space, application of lighting equations, bounding box computation, and pre-filtering - has been integrated. The implementation applies real-valued single-precision floating-point arithmetic, providing the base for a system throughput of 3.4 million splats per second. This VLSI design uses extensive resource sharing, hence reducing the overall core area to 8.16 mm2 in a 0.18 mm CMOS technology. In this work, we present - to the best of our knowledge - the integrated solution reaching the highest ratio between throughput and silicon area, above all previously published EWA implementations.