The IIS Chip Gallery

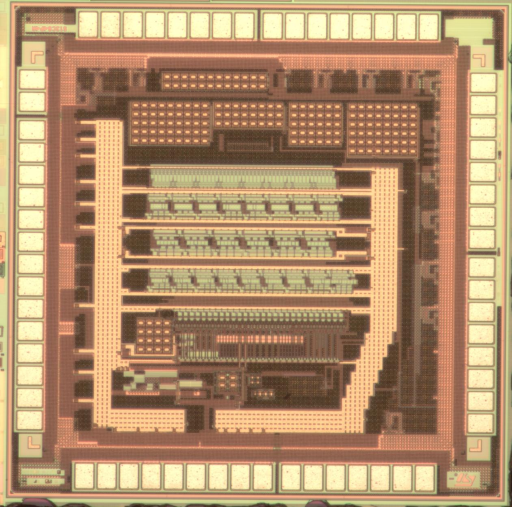

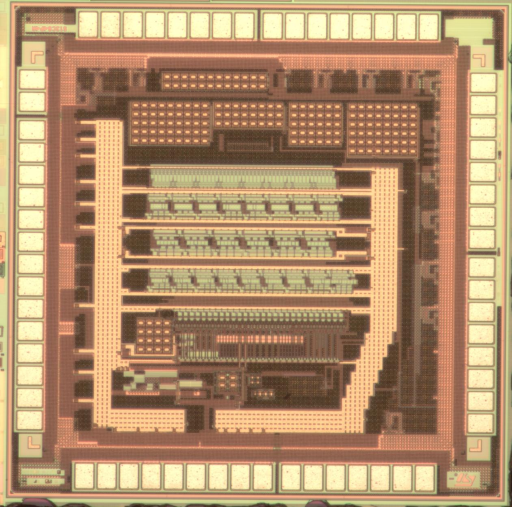

Folding_ADC (2008)

by

In recent years, unrelenting growth in digital communications, multimedia, and other consumer products has translated into increasing demands for analog-to-digital converters (ADCs) with 8-10 bits resolution and sampling rate in excess of 100 MSample/s.

Folding and interpolating architecture inherits speed advantages from flash one, and usually only needs low complexity building blocks, which makes it attractive for mainstream CMOS processes. However, its resolution is severely limited by the poor matching properties of the differential pairs and current mirrors. The interpolating and averaging techniques improve linearities, but fairly large transistors are indispensable to keep the offset low, which limits the achievable speed with a fixed power budget.

This project employs an innovative digital calibration technique, which directly measures the offsets of preamplifiers and first stage folding amplifiers from raw digital codes of the folding ADC core, and accomplishes corrections in digital domain. This scheme only adds a few additional analog elements, but relaxes the matching requirements on the aforementioned amplifiers substantially. As a result, those amplifiers can be realized with smaller transistors, which improves the speed-accuracy-power trade-off. A prototype circuit has been fabricated in a 0.13um CMOS technology with a supply voltage of 1.2 V.