The IIS Chip Gallery

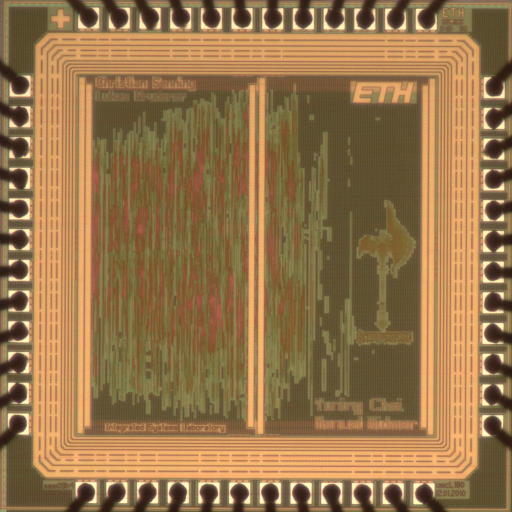

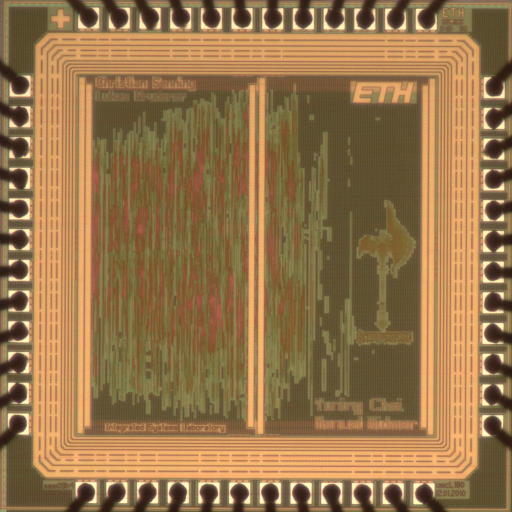

Shadowmourne (2009)

by

| Application | Processor |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 80 kGE |

| Voltage | 1.8 V |

| Clock | 265 MHz |

In state-of-the-art MIMO wireless links, thermal noise is introduced into the transmit and the receive chain. Recently, measurements have shown that transmit-side noise can not be neglected since the assumption of spatially uncorrelated noise at the receiver does no longer hold. Spatially-colored noise has detrimental effects on the error-rate performance of certain (near-) maximumlikelihood decoders (e.g., sphere decoder (SD) and Kbest decoder).

The goal of this project was to design the preprocessing stage with noise whitening filter computation for SDbased detectors. Recently, it was suggested that the computation of the whitening filter for the colored noise can be efficiently implemented by a regularized QR decomposition, and two complex-valued matrix multiplications. These three steps have to be done additionally to a sorted QR decomposition of the equivalent channel (i.e., whitened channel) required for the detector. To accommodate the necessary preprocessing steps, a processor architecture capable of QR decomposition based on the modified Gram-Schmidt algorithm was realized.

The design was implemented in a 180 nm (1P/6M) CMOS process and occupies 79 kGE. The resulting ASIC operates at a maximum clock speed of 270 MHz while achieving a sustained throughput of 0.6 million complex-valued 4x4-dimensional channel matrices per second.