The IIS Chip Gallery

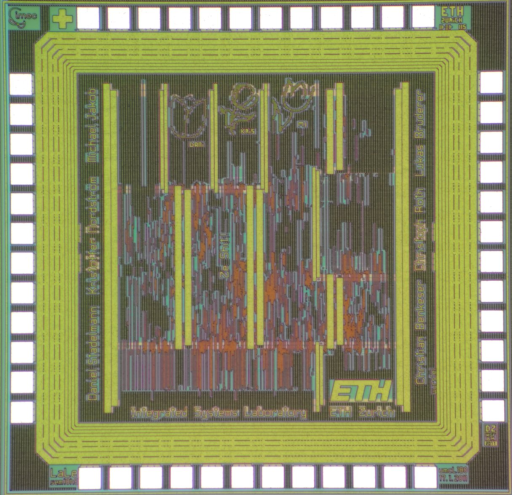

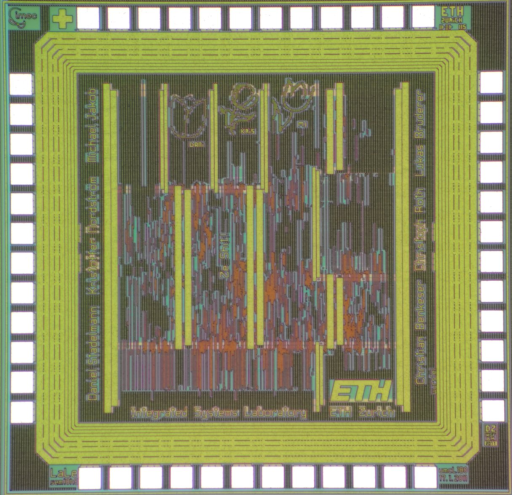

LaLe (2010)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 70 kGE |

| Voltage | 1.8 V |

| Clock | 100 MHz |

Turbo Decoder Implementation for Evolved EDGE

The high throughput and quality-of-service requirements of today's wireless communication systems require highly reliable communication links. Considering the hostile environment these systems operate in, employing a high-performance error-correction is often a last resort to meet the stringent requirements. In this context, low-density parity check (LDPC) codes have become more and more the focus of attention recently due to their excellent error-correction capabilities. Especially, the subclass of quasi-cyclic (QC) LDPC codes oers high decoding throughput at relatively low implementation complexity and has been included in several new-generation wireless standards, e.g., IEEE 802.11n, IEEE 802.16e, or DVB-S2. Considering the growing use of QC-LDPC codes, it is striven for a simple and highly scalable architecture that can be constrained during design time to a certain standard or used as a multi-standard design.

Due to the high mobility of modern wireless communication systems, power has become a major issue that influences their design at an early stage. It is a challenging task to come up with low-power decoders while achieving the high requirements in terms of throughput.

LaLe is a low-power VLSI implementation of a QC-LDPC decoder complying with today's throughput requirements. Based on the congurable high- throughput reference design, several low-power strategies are incrementally introduced and evaluated. The goal is to create a highly competitive design in terms of power and throughput that exhibits nice scaling properties, rendering the design suitable for a multi-standard solution. While both standards IEEE 802.11n and IEEE 802.16e are considered in this work, the presented designs are optimized for the IEEE 802.11n stan- dard. The introduced low-power strategies are applied on various levels of abstraction, from the algorithmic one down to the gate level.