The IIS Chip Gallery

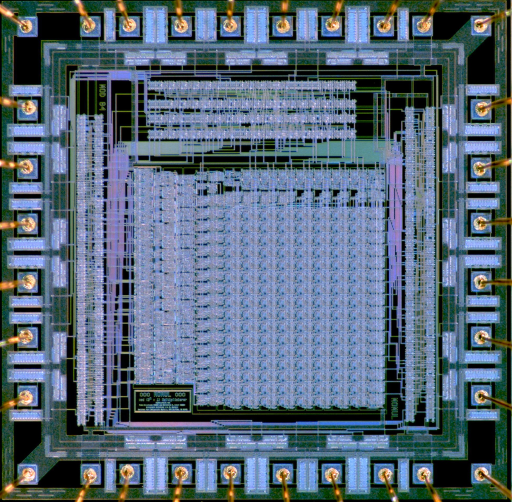

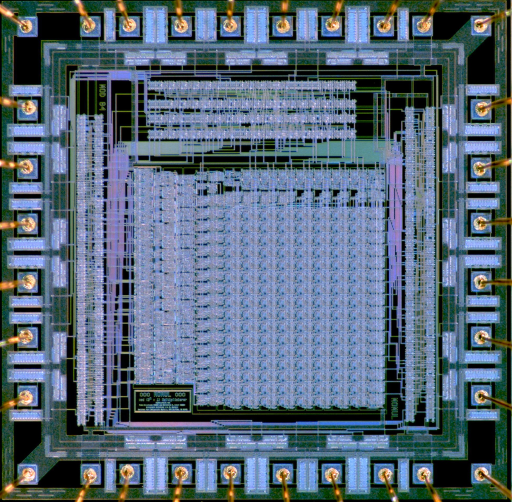

MOMUL (1990)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 1500 |

| Manufacturer | VLSI Tech |

| Type | Semester Thesis |

| Package | DIP40 |

| Dimensions | 3200μm x 3200μm |

| Gates | 3500 |

| Voltage | 5 V |

| Power | 46 mW |

| Clock | 25 MHz |

A 16-bit multiplier modulo (2^16+1) has been developed for the new IDEA-cryptography chip. This multiplier has been implemented as a two stage pipeline and realised in full custom layout to achieve high speed and small area requirement. It has been integrated on a special chip together with some test structures.

The chip has been successfully tested and a delay of 36.1ns at 5V supply voltage has been measured. Two out of ten fabricated chips were faulty and the faults have been localized. The power consumption is about 1uW in the static and 46mW in the dynamic case (@25 Mega Multiplications per second).

In a redesign, the multiplier speed has been nearly doubled by improving the layout and porting it to a denser and faster technology.

The design has been fault simulated on gate and transistor level. In addition to several tenth of random patterns, three special vectors are needed to get a fault coverage of at least 99%. These vectors have been hard coded at the multiplier inputs to ease testing.