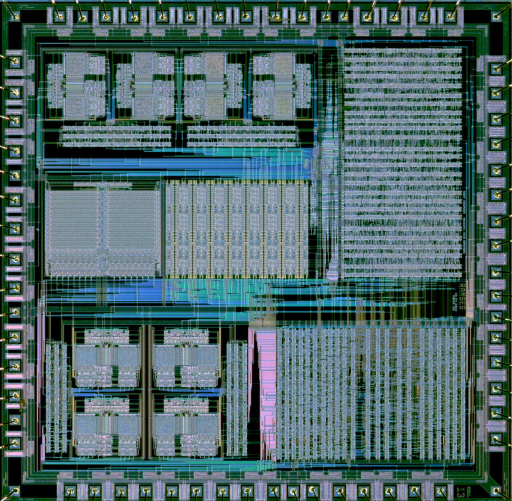

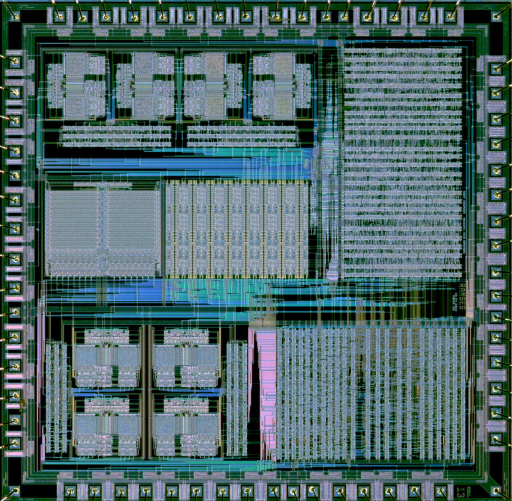

The IIS Chip Gallery

Ramses (1990)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 1500 |

| Manufacturer | VLSI Tech |

| Type | Research |

| Package | PGA88 |

| Dimensions | 6300μm x 6400μm |

| Gates | 25 kGE |

| Voltage | 5 V |

| Power | 800 mW |

| Clock | 25 MHz |

The Ramses (Rapid And Maximal Secure Encryption System) Chip is a cryptography micropocessor peripheral device implementing an 8-bit variant of the new secret key block cipher by Lai and Massey (ISI).

RAMSES operates on 64-bit data blocks and uses a 128-bit user specified key to produce 64-bit cipher blocks. The operation is reversible: i.e. an encrypted block is converted to the original plaintext block if the inverted key is applied. The complete ciphering process is performed on chip; no intermediate results are stored off-chip.

To achieve a high data encryption rate, the chip datapath consists of a variable 7-9 stage pipeline, which is run through 12 times per block encryption. An 64-bit input register allows the pipeline to be permanantly fully loaded.

The chip has been fabriacted and tested successfully. The maximum encryption rate is 61 Mbit/s (@ 25MHz chip clock) at a power consumption of 0.8W. The 90'000 transistors use 6.3mm x 6.4mm silicon area in a 1.5um double metal CMOS process.