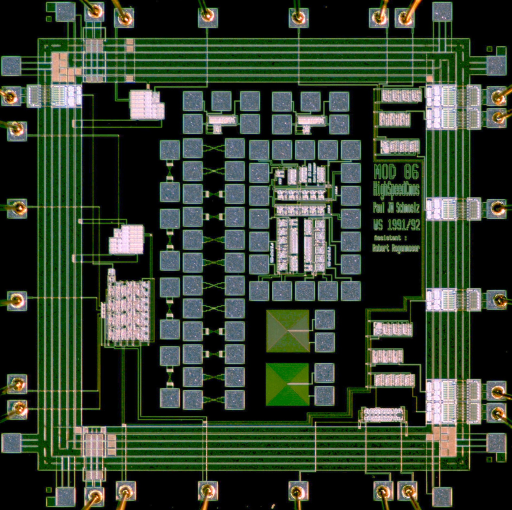

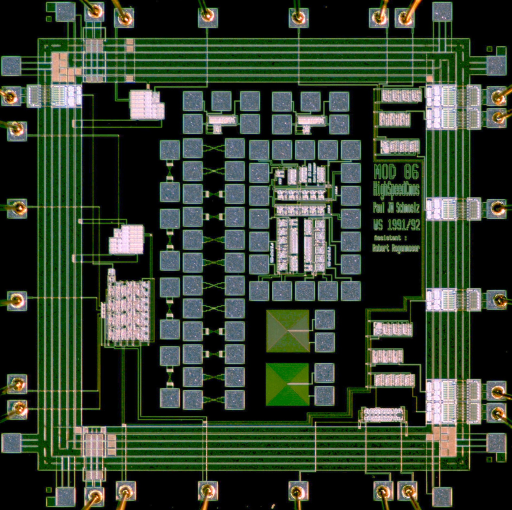

The IIS Chip Gallery

Frequency_divider (1991)

Additional pictures below, click to see larger versions

by

| Application | Industrial |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Diploma Thesis |

| Package | DIP24 |

| Dimensions | 6900μm x 6200μm |

| Voltage | 5 V |

| Clock | 475 MHz |

In this project a series of fast asynchronous dividers based on the dynamic Svennson and Huang Flip-Flop have been realized. A programmable frequency divider has been implemented with the help of additional logic. Other blocks include a programmable ring oscillator. This technique allowed speeds of up to 500MHz on chip.