The IIS Chip Gallery

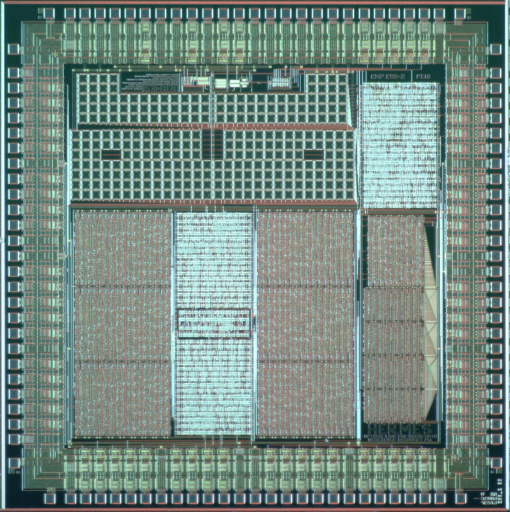

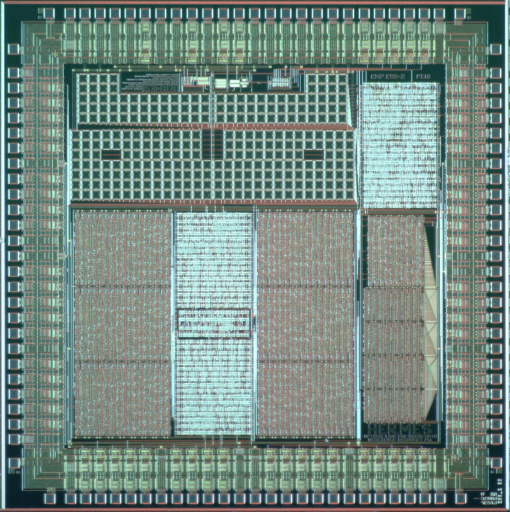

Hermes (1998)

by

| Application | Audio |

| Technology | 800 |

| Manufacturer | ES2 |

| Type | Semester Thesis |

| Package | PGA100 |

| Dimensions | 5000μm x 5000μm |

| Gates | 16 kGE |

| Voltage | 5 V |

| Clock | 45.1548 MHz |

The HERMES ASIC combines a 16-channel transmitter and a 2-channel receiver on one chip. The 16 standard I2S digital audio inputs are multiplexed to a modified AES/EBU signal format. The modification concerns the eight-fold standard data rate with channel identification.

The receiver part can run in parallel to the transmitter if bidirectional communication is required. It contains a Phase-Locked-Loop (PLL) with external crystal for sampling clock recovery (11 MHz). The quality of this clock determines the effective number of usable bits in a digital system. A maximum of 20 ns rms jitter is allowed for reaching the full quality of the 20 transmitted bits per sample. An additional digital PLL provides the 44 MHz system clock required for operating the digital part of the receiver.

The chip has been developed for a standard digital CMOS technology. The missing double-poly capacitors and the low bulk resistance make the mixed signal design a real challenge.