The IIS Chip Gallery

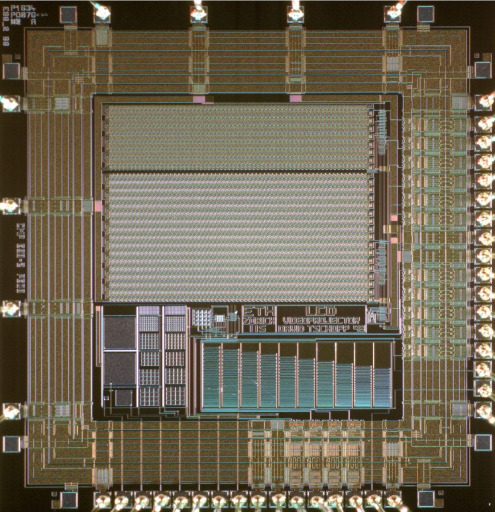

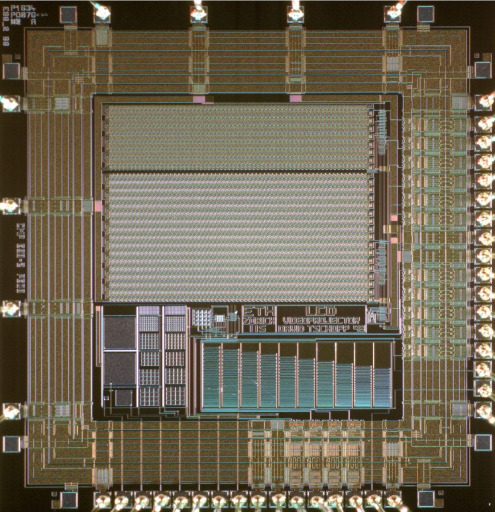

LCD (1998)

by

| Application | Graphics |

| Technology | 500 |

| Manufacturer | Philips |

| Type | Semester Thesis |

| Package | Unknown |

| Dimensions | Unknown |

In Liquid-Crystal-On-Silicon (LCOS) technologies the electro-optic liquid crystal is brought in direct contact with the silicon integrated circuit using the topmost metal as backside electrodes. Resulting displays are expected to have a high modulation depth and to be fast and compact. Additionally the spatial resolution benefits from advances in silicon technologies.

Most published LCOS displays use memory-like array loading of image data. This implies a high pin count and limits the achievable array size.

The goal of this project was to develop better display architectures by incorporating more processing logic into each pixel and thus making it smart. Consequently the pin count decreases. Our design targeted large displays (>1000 x 1000 pixels) with a modulation depth of more than 256 gray levels and a picture frame rate of at least 50 Hz.

After evaluating a couple of possible approaches we opted for an architecture that uses shift registers for data storage. Gray levels are generated by using binry-weighted pulse distances on the clock line that controls downloading to the pixel electrodes.

By careful layout a pixel size of 20 x 20 mm2 was achieved using a 0.5 mm 2-metal CMOS process. Silicon prototypes containing rows with more than 1000 pixels have been produced and measured. The electrical results even exceeded our design goals.