The IIS Chip Gallery

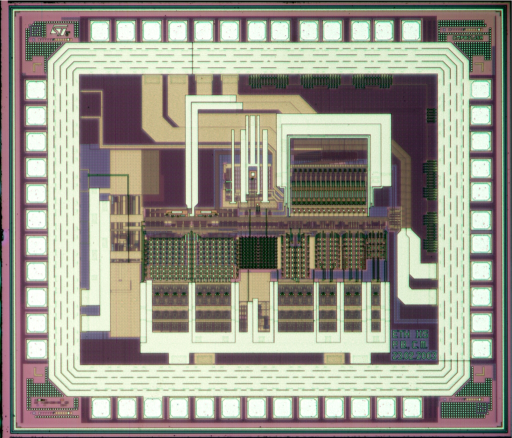

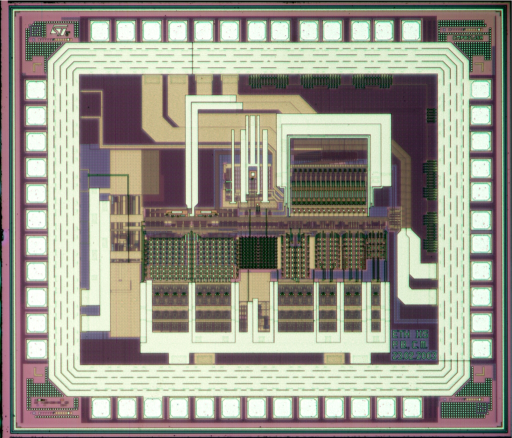

VDSL_Sigma_Delta (2003)

by

| Application | Converter |

| Technology | 180 |

| Manufacturer | STM |

| Type | Research Project |

| Package | LCC44 |

| Dimensions | 1200μm x 1000μm |

| Voltage | 1.8 V |

| Power | 203 mW |

The increasing demand for broadband Internet access and the growing use of digital processing forsters the implementation of communications standards employing sophisticated decoding methods capable of achieving high data rates using existing communications media. However, the trend towards higher data rates and digital signal processing increases the dynamic range and the bandwidth required at the A/D interface. VDSL is one of these standards, it uses the plain old telephone services for transmitting data at a maximum rate of 30Mbps.

Oversampled Sigma Delta ADCs are highly suited for high resolution integrated circuit implementations since they do not need a precision S/H stage, have relaxed requirements for the anti-aliasing filter, and achieve very good linearity despite the use of imprecise building blocks. However, the need of oversampling reduces the achievable conversion rate.

The designed Sigma Delta modulator has a discrete-time, singleloop architecture. The loop filter has a feed-forward topology and employs a 4bit quantizer. The oversampling ratio is 8. To linearize the 16 level feedback DAC, dynamic element matching is used. The circuit has been implemented in a mainstream 0.18um digital CMOS technology with 1 poly and 6 metals. The supply voltage is 1.8V. The core area is 0.95mm2. The power consumption is 203mW. With 25MS/s conversion rate and 82dB signal-to-noise, this circuit outperforms in speed and resolution combination any previously published Sigma Delta modulator.