The IIS Chip Gallery

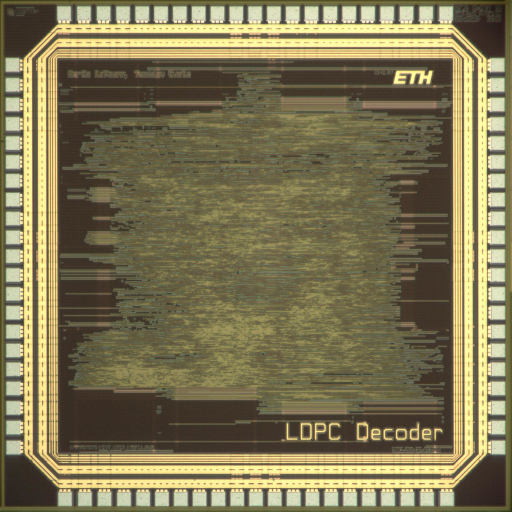

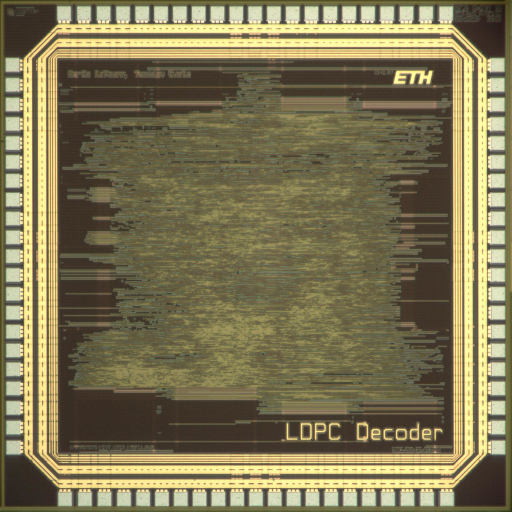

LDPC_decoder (2006)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 2.5 V |

| Clock | 140 MHz |

Low-density parity check (LDPC) codes have been shown to achieve excellent error rate performance close to the Shannon limit. The original idea has already been discovered by Gallager in 1962. Unfortunately, at that time, its codes were deemed to complex for efficient decoder implementations. Almost 30 years later, the codes were rediscovered and the tremendous advances in silicon process technology have enabled the integration of high-speed LDPC decoders in VLSI. Consequently, LDPC codes are under consideration for a number of most relevant wireless communication systems, most notably for the IEEE 802.11n standard for wireless local area networks.

The goal of this project has been to develop an area-optimized decoder ASIC for the systematic LDPC code specified by the IEEE 802.11n draft proposal. The developed circuit implements the message passing algorithm on a moderately parallel VLSI architecture that stores the messages in memories. The main challenge in the design was to exploit the structure of the code to alleviate the memory- access bottleneck that limits the amount of parallel processing and thus the throughput of the design.

The manufactured ASIC achieves a decoding throughput of 17 Mbps with eight decoding iterations and 46 Mbps with three iterations. Its AT-product is comparable to faster, but also much larger ASIC implementations.