The IIS Chip Gallery

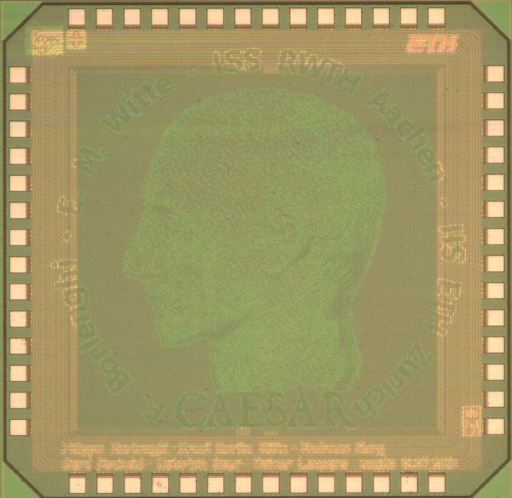

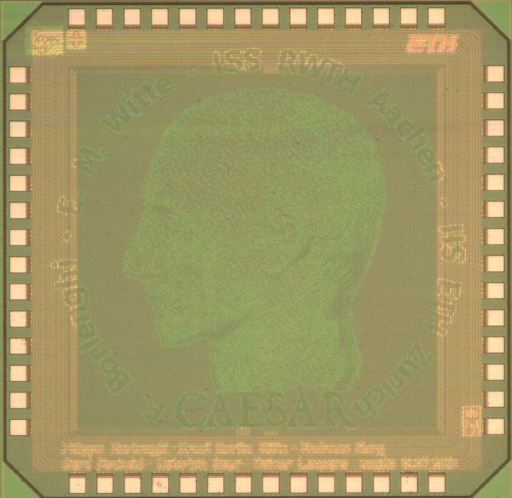

Caesar (2010)

by

| Application | Communication |

| Technology | 90 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | QFN56 |

| Dimensions | 1875μm x 1875μm |

| Gates | 400 kGE |

| Voltage | 1.0 V |

| Power | 86 mW, 1V |

| Clock | 193 MHz |

Future wireless communication systems require on the one hand increasing data rates and on the other hand operating in worse channel conditions. Combining Multiple-Input Multiple-Output (MIMO) techniques and iterative detection-channel decoding allows to cope with these conflicting requirements.

However, iterative MIMO detectors have been so far too complex for VLSI implementation, especially when considering max-log-MAP optimal algorithms such as sphere decoding. The Caesar chip, fabricated in 90nm UMC technology, is the first implementation of a soft-input soft-output single-tree search sphere decoder.

The architecture is configurable in terms of number of antennas and modulation scheme; furthermore, various run-time constraints can be configured in order to trade-off BER performance against throughput, which is variable, and energy efficiency.

Three cores have been integrated on the chip, supporting up to 4x4 antennas and up to 4, 16 and 64 QAM modulations respectively. The 64-QAM instance occupies an area of 0.665 mm˛ (212 kGE) and runs at a maximum frequency of 193 MHz. The corresponding maximum uncoded throughput is 772 Mbps for 4-stream MIMO, since the detection requires a minimum of (number of antennas + 2) cycles. In this case, which happens in good channel conditions, the power consumption is 86 mW at 1 V supply voltage, leading to a minimum energy cost of 0.11 nJ/bit.

This chip is a collaboration with the ISS RWTH Aachen.