The IIS Chip Gallery

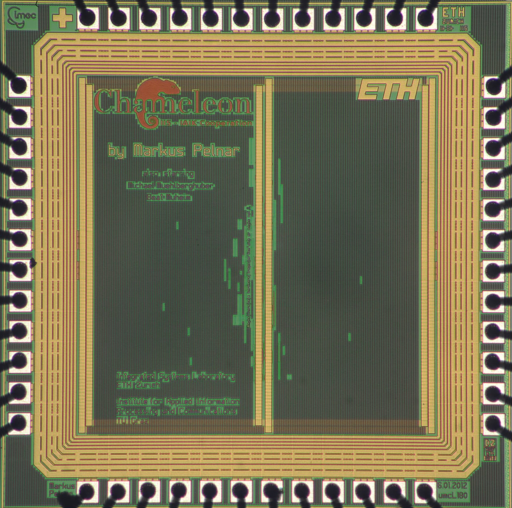

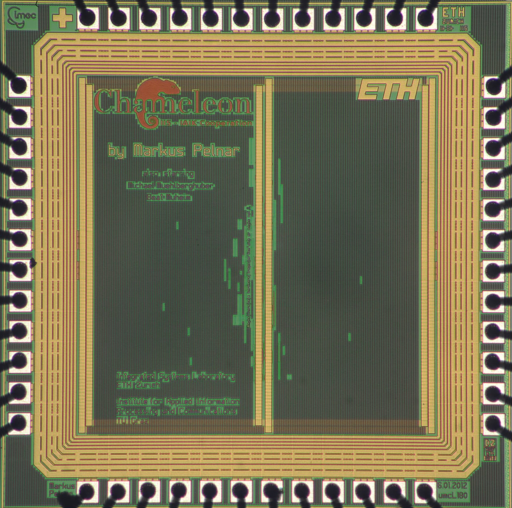

Chameleon (2011)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Master Thesis |

| Package | QFN56 |

| Dimensions | 1525μm x 1525μm |

| Gates | 40 kGE |

| Voltage | 1.8 V |

| Power | 21 mW, 100MHz |

| Clock | 125 MHz |

GrAEStl combines AES-128 and Groestl-224 in one hardware architecture targeting low area and high flexibility regarding ASIC and FPGA design flows. Therefore, no technology or platform-dependent components such as RAM macros, DSPs, or Block-RAMs have been used. Furthermore, GrAEStl includes standalone variants for AES-128 and Groestl-224 in order to provide a fair comparison between the combined and the standalone versions of both cryptographic primitives. An AES encryption/decryption takes 735/1,350 cycles for both the standalone and the combined implementation. For the combined version a cycle reduction for the decryption can be achieved if an encryption/decryption with the same cipher key has been applied before. If so, the cycle count reduces to 1,025. For Groestl both variants require 3,067 cycles for hashing one message block of size 512 bits. The combined version occupies only 17 kGE whereas the single variants for AES and Groestl occupy 5kGE respectively 16kGE including clock gating and eight scan chains. The power consumption for the combined version is 20mw for an AES encryption/decryption respectively 21mw for a Groestl hash operation. The standalone versions for AES and Groestl consume 14mW respectively 20mW.