The IIS Chip Gallery

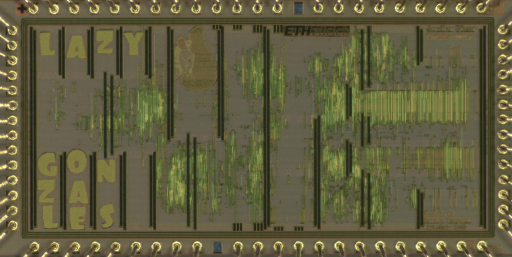

LazyGonzales (2013)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN56 |

| Dimensions | 3240μm x 1525μm |

| Gates | 200 kGE |

| Voltage | 1.8 V |

| Power | 147 mW, 100MHz 1.8V |

| Clock | 322 MHz |

In this project a turbo decoder employing shuffled decoding with non-aligned half-iterations has been implemented in an ASIC on the basis of the LTE/LTE-Advanced standard. Since LTE-Advanced requires an enormous throughput of up to 3 Gbps and specifies a wide range of code rates and block-sizes of up to 6144 bit, a fully standard-compliant ASIC requires a large silicon area and possibly an advanced CMOS-process. We therefore only realize a proof-of-concept chip containing 2 SISO-decoder cores, which demonstrates the concept of shuffled decoding and proves that it is indeed feasible.

The chip achieved 81.2 MB/s decoding rate during tests

If more units were to be instantiated this architecture could achieve a very high throughput. However, this version is not as fast as it could be. Therefore it is not Speedy but Lazy Gonzales.