The IIS Chip Gallery

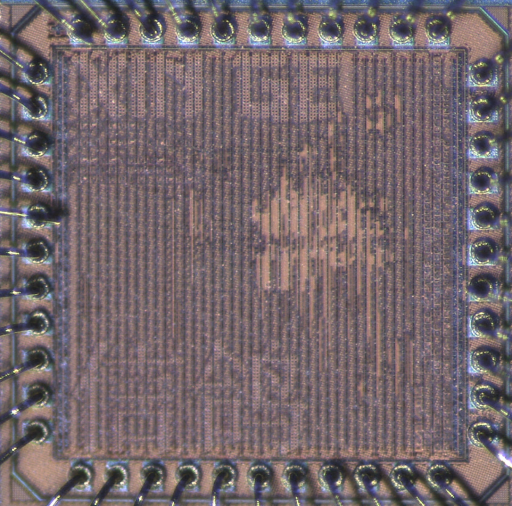

XinGe (2014)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN40 |

| Dimensions | 1252μm x 1252μm |

| Gates | 500 kGE |

| Voltage | 1.2 V |

| Power | 140 mW @ 1.2 V, 325 MHz |

| Clock | 325 MHz |

This chip implements a constrained Viterbi algorithm (CVA) equalizer for near-maximum likelihood sequence estimation (MLSE) in the downlink of code division multiple-access (CDMA) mobile communication systems. It is designed to support the time-duplexing high speed packet access (TD-HSPA) mobile communication standard and is one of the two main components in IIS' novel LEG-CVA [1] detector. When configured to use 64-QAM the chip can achieve decoding throughputs up to 4.2 Mbit/s, as specified by the TD-HSPA standard.

China's mobile communication market contributes a large deal to TD-HSPA's booming global market development. The chip was thus given the Chinese name for a carrier pidgeon, namely "Xin Ge", and carries the corresponding Chinese characters.