The IIS Chip Gallery

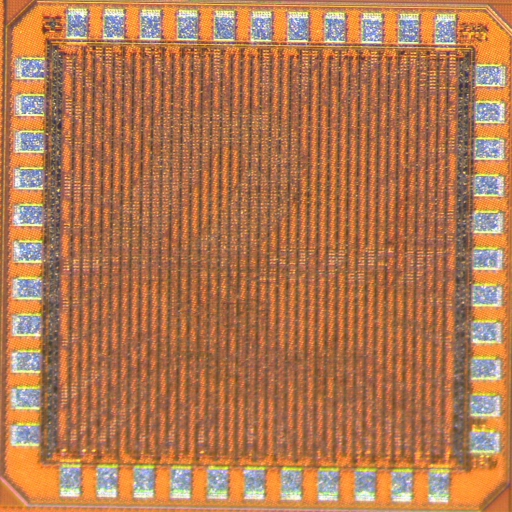

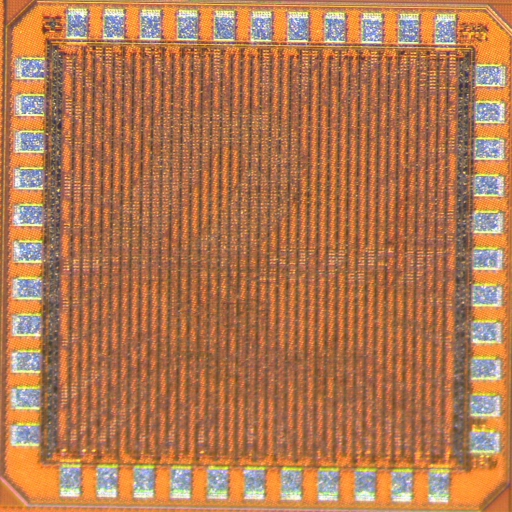

Drift (2018)

Additional pictures below, click to see larger versions

by

| Application | Processor |

| Technology | 65 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | QFN40 |

| Dimensions | 1252μm x 1252μm |

| Gates | 200 kGE |

| Voltage | 1.2 V |

| Power | 999 mW @ 0.2 V, 1 MHz |

| Clock | 600 MHz |

This chip is made for wannabe race drivers that are too lazy to learn proper driving techniques. When glued to the steering wheel, it will turn even the tamest car into a drift king.

This chip implements several different integer divider architectures that can be used as part of the 64-bit RISC-V core Ariane. It contains several versions. Standard non restoring division, SRT Radix2, SRT Radix4 as well as a pipelined parallel array divider for comparison. The chip contains a random vector generator as well as a LUT with selected inputs to test all multipliers at speed.

The name stands for Division with different Radix representations of Integers using Fractional Transformation.