The IIS Chip Gallery

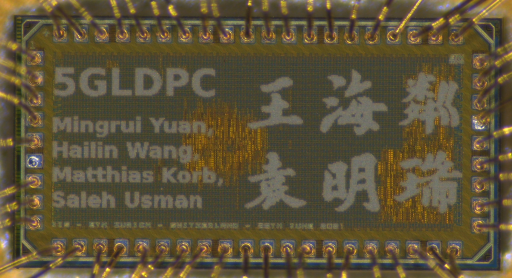

5GLDPC (2021)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 65 |

| Manufacturer | TSMC |

| Type | Research |

| Package | QFN56 |

| Dimensions | 2000μm x 1000μm |

| Gates | 1600 kGE |

| Voltage | 1.2 V |

| Power | 4 kW @1 MHz mW |

| Clock | 200 MHz |

Small test chip implementing the Low Density Parity Code decoder/encoder for the 5G standard.

The logo contains the names of the students that worked on it (Mingrui and Hailin), in their native language.