The IIS Chip Gallery

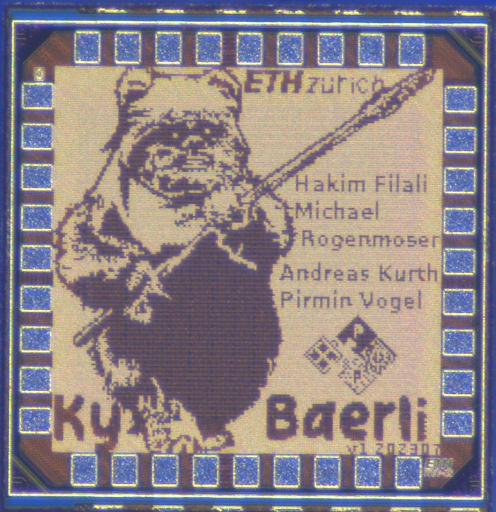

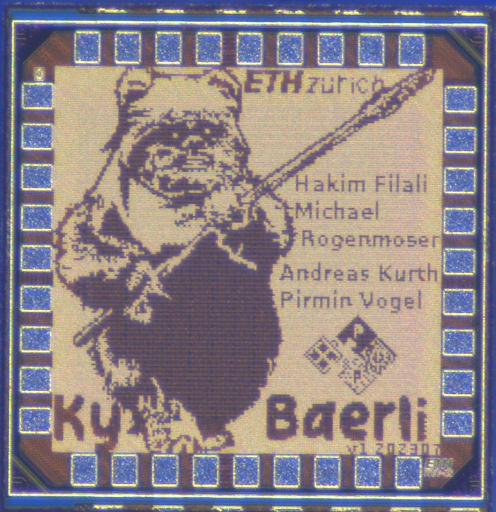

Kybaerli (2023)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 65 |

| Manufacturer | TSMC |

| Type | Research |

| Package | QFN40 |

| Dimensions | 1000μm x 1000μm |

| Gates | 250 kGE |

| Voltage | 1.2 V |

| Power | 12345 mW @1 MHz |

| Clock | 315 MHz |

This design focuses on the implementation and optimization of a hardware accelerator for polynomial multiplication, specifically aimed at enhancing the performance of the KYBER Key Encapsulation Mechanism (KEM) algorithm. The CRYSTALS Kyber KEM is one of four PQC algorithms selected for standardization by the National Institute of Standards and Technology (NIST).

By leveraging the Number Theoretic Transform (NTT), which is a discrete Fourier Transform on a Ring, this work achieves a significant reduction in latency for the polynomial multiplication. The NTT enables a coefficient-wise multipli-cation in the frequency domain with a reduced time complexity of O(nlogn). To further enhance efficiency, the design incorporates parallelization techniques and employs a specialized memory access pattern to improve pipelining. Additionally, architectural enhancements are applied to arithmetic sub-blocks to increase the achievable operating frequency.

The name is a play on the name of the algorithm Kyber, the fact that the way the last syllable is pronounced sounds like a bear and the tendency of Swiss German speaking people adding '-li' to the end of words to make them diminutive. The result is to have an Ewok from the Star Wars universe as the logo.