The IIS Chip Gallery

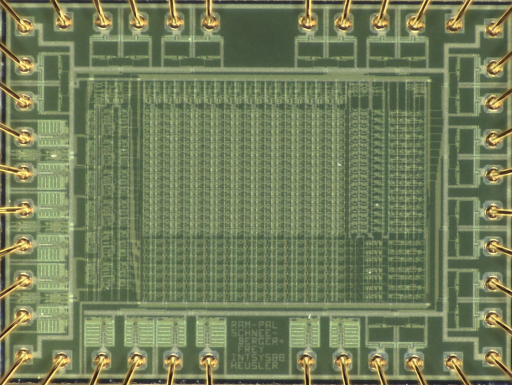

Universal_PAL (1987)

Additional pictures below, click to see larger versions

by

| Application | Industrial |

| Technology | 3000 |

| Manufacturer | Faselec |

| Type | Semester Thesis |

| Package | DIP40 |

| Dimensions | 3200μm x 2400μm |

| Gates | 1400 |

| Voltage | 5 V |

| Clock | 12 MHz |

This chips implements a Programmable Logic Array with 10 inputs, 6 programmable outputs. It uses 408 program bits and a PLA organization (AND-OR plane). A separate input is used to scan in the configuration.