The IIS Chip Gallery

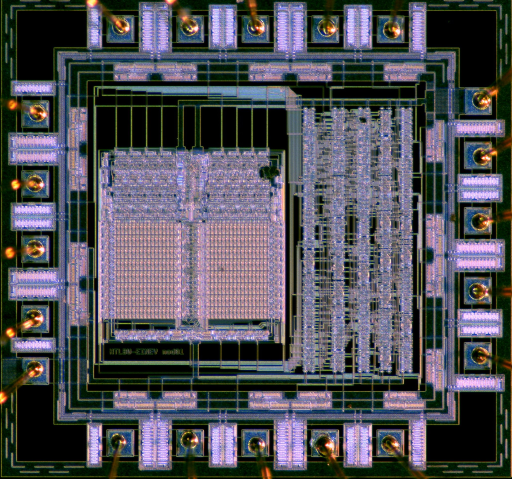

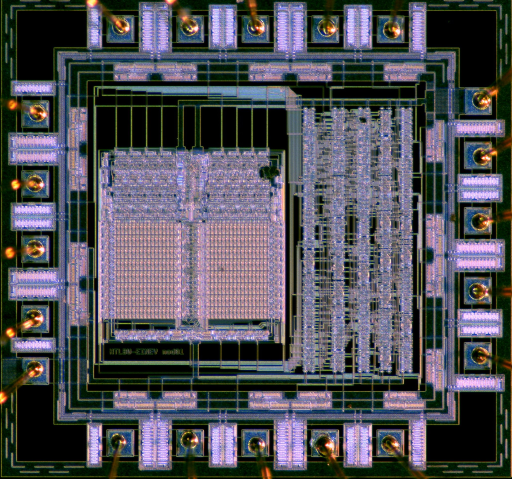

FIFORam (1992)

by

| Application | Industrial |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Research |

| Package | DIP24 |

| Dimensions | 3200μm x 3200μm |

| Gates | 1600 |

| Voltage | 5 V |

| Power | 20 mW(30 MHz, 5V) |

| Clock | 35 MHz |

There have been several FIFO RAMs that were designed at IIS. The design was popular for design courses and proved to be a good exercise. Over the years, some deliberately faulty chips were also manufactured and used as part of VLSI III test exercises. It is sometimes difficult to pinpoint which chip is made when and by who, but the data for this chip seems to be accurate.

The FIFORAM chip is a First-in First-Out memory of 64 bytes depth. Read and write operations, in contrast to conventional FIFOs are performed over the unique bidirectional port. Separate read and write pins control the data access and the chip selection. Status information is avilable from the empty, full and error pins. Writing the full FIFORAM, reading the empty FIFORAM and simultaneous read and write acc4ess lead to the error condition which can only be cleared by applying a reset signal.

The FIFORAM built-in test support circuitry allows the user to test the chip on the PCBoard by use of three test modes enabled by testselect inputs.