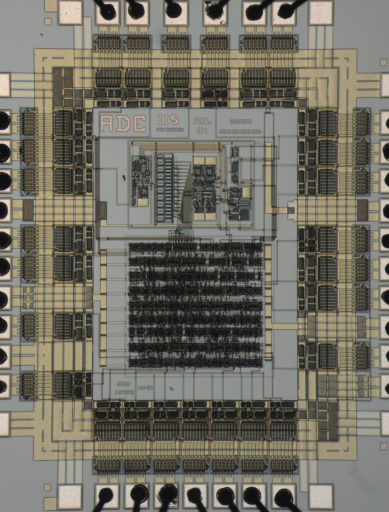

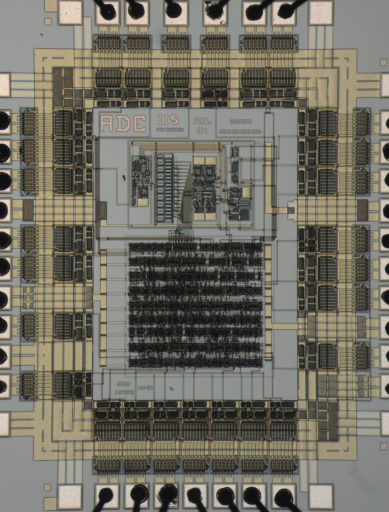

The IIS Chip Gallery

ADC (1993)

by

| Application | Converter |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Master Thesis |

| Package | DIP40 |

| Dimensions | 3100μm x 3100μm |

| Voltage | 5 V |

Building analog blocks and subsystems in digital process technologies has many advantages, e.g. implementing analog preprocesisng circuitry and digital signal processing components on a single chip. Using a purely digital technology decreases the cost for integration substantially. The challenge with this approach is to cope with a technology developed for digital circuits and therefore lacking high-quality passive components.

This partiular design implements a successive approximation analog to digital converter. This technique offers conversion at medium speed and medium resolution on a moderate amount of silicon area.

The critical part in successive approximation architecture is a digital analog converter. It has been implemented using a MOS-transistor only R-2R ladder structure. Current summation at the output of the ladder is accomplished by a regulated cascode amplifier which provides very low impedance input nodes that are well suited for this purpose.

The design includes additionally a low-offset current comparator, an input amplifier and a fully synchronous digital controller which essentially implements the successive approximation register.