The IIS Chip Gallery

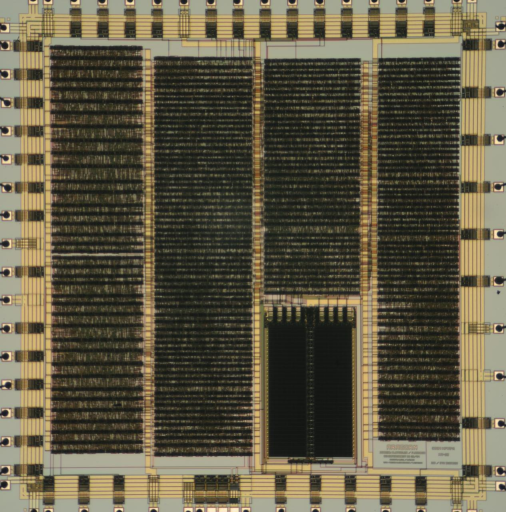

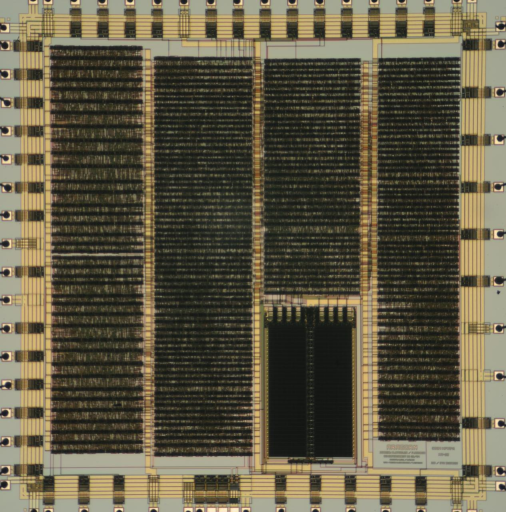

Aragorn (1993)

Additional pictures below, click to see larger versions

by

| Application | Communication |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Semester Thesis |

| Package | PGA84 |

| Dimensions | 6040μm x 6280μm |

| Gates | 18 kGE |

| Voltage | 5 V |

| Clock | 23 MHz |

Future transmissions of digital audio, digital video or data transfer on existing two-wire copper lines is an alternative to costly high-quality, high-speed data links. The data transfer rate in HDSL (High-bit rate Digital Subscriber Line) systems is 2 Mbit/s. carrierless amplitude and phase modulation (CAP) and 2B1Q (2 binary 1 Quarternary) are used to transmit digital data on two wire copper lines with a channel rate of 1.5 Mb/s.

The 2 Mb's data stream is split in two channels. Each channel is formatted in so-called frames. Each frame consists of 700 bits including synchronization, data and CRC (Cyclic Redundancy Check) bits. The receiver part of the chip has to match two 1.5b/s channels into one 2 Mb/s data stream.

A single chip acts as sender and receiver. It stores the incoming data and corrects fluctuations of the bit rates, as the clocks for the inputs and the output side come from different sources. Teh real challenge for this chip design was the synchronization of all the incoming signals and clocks.