The IIS Chip Gallery

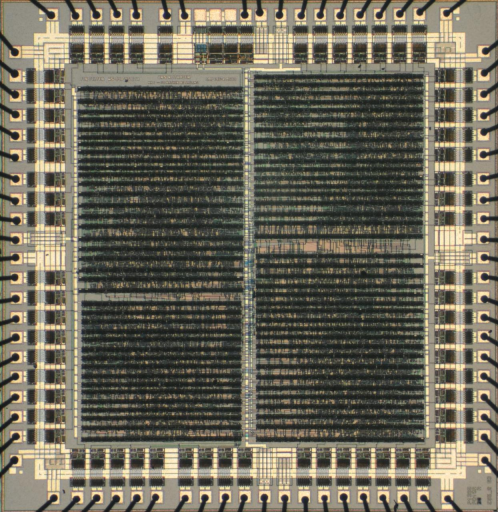

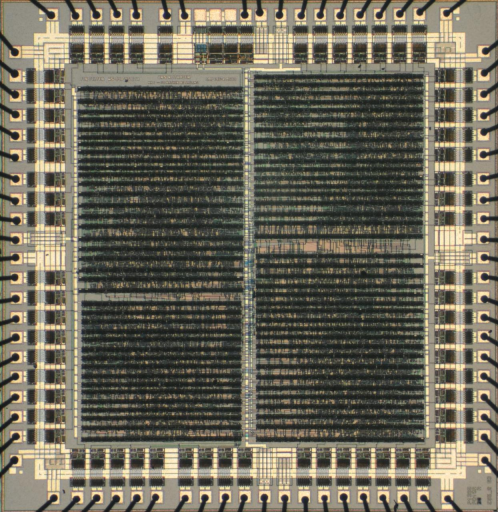

KA1 (1994)

by

| Application | Filter |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Semester Thesis |

| Package | PGA84 |

| Dimensions | 4500μm x 4400μm |

| Gates | 10 kGE |

| Voltage | 5 V |

| Clock | 60 MHz |

High-performance wireless LANs with data rates up to 25MHz suffer heavily from multipath propagation, which is typical for indoor environments. The resulting intersymbol interference can be reduced by using adaptive equalizers at teh receiver side. These can be immplemented by transversal filters with the coefficients being adapted to the characteristics of the transmission channel.

This application asks for an FIR filter with an 8-bit complex inputs and coefficients, 8 to 13 taps and a sample rate of 25 Msamples/s. This ASIC was developed to fulfill these requirements, but due to area limitations only 4 stages could be implemented in one chip. However the design allows multiple chips to be cascaded, and by using 4 chips a 16 tap filter with the desired accuracy and speed can be implemented.

the ASIC is controlled via a processor interface, and the filter coefficients can be updated online. Deciacted complex multipliers were developed, which make use of Booth-encoding and Wallace-tree speed up techniques in order to achieve the desired throughput. Internal calculations are made using 22-bit operands.Output scaling and saturation functions were also included.

The chip was shown to be operational at clock speed of up to 60 MHz, resulting in a throughput of 30 Msymbols/s. This work was done in collaboration with ASCOM.