The IIS Chip Gallery

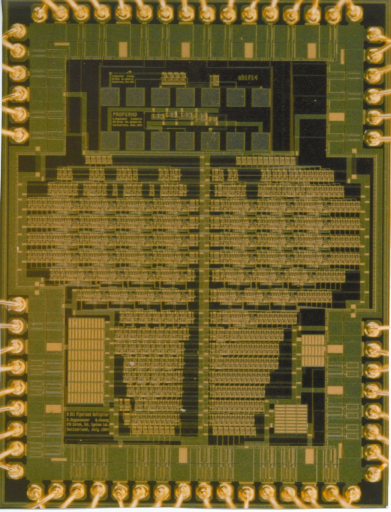

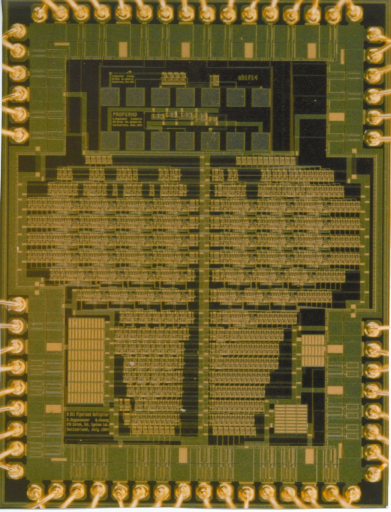

Propermo (1994)

by

| Application | Processor |

| Technology | 1000 |

| Manufacturer | Faselec |

| Type | Research Project |

| Package | DIP64 |

| Dimensions | 2000μm x 3300μm |

| Gates | 3 kGE |

| Voltage | 5 V |

| Power | 3.2W(375 MHz, 5V) mW |

| Clock | 375 MHz |

A signed 8-bit pipelined multiplier has been implemented in a standard 1.0 pm CMOS process. It was successfully tested up to 375MHz. This performance was achieved using the true single-phase clocking technique, fine-grain pipelining, and merging the combinational logic into the pipeline registers.

The data throughput of 375 million multiplications per second is achieved using fine-grain pipelining, merging the combinational logic into the pipeline registers, and by careful transistor sizing. The cost of this approach is an increased latency. As applications working on large streams of data are limited in their performance by the throughput rather than latency, the latter is often of minor concern. Furthermore, less parallel processing units are required to maintain throughput in low power applications if fast building blocks are used. This alleviates the partitioning of algorithms into many parallel tasks.