The IIS Chip Gallery

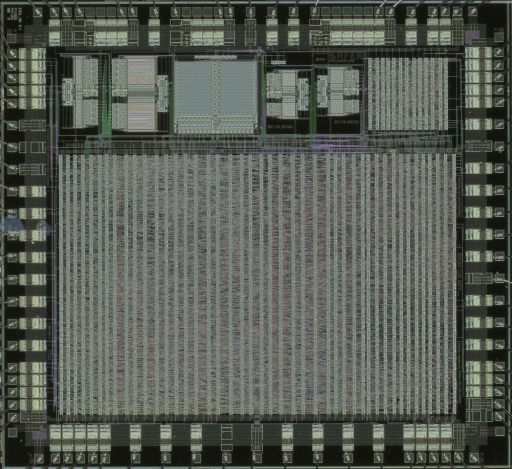

Safer (1995)

Additional pictures below, click to see larger versions

by

| Application | Cryptography |

| Technology | 1200 |

| Manufacturer | VLSI Tech |

| Type | Semester Thesis |

| Package | PGA84 |

| Dimensions | 6300μm x 6300μm |

| Gates | 20 kGE |

| Voltage | 5 V |

| Clock | 20 MHz |

By the end of 1995, Prof. J massey of ETHZ had finalized a non-proprietary cipher called SAFER, an acronym that stands for "Secure and Fast Encryption Routine". The underlying algorithm is based on byte operations and implements a set of secret-key iterated block ciphers with a block length of 64 bits. Members of that family differ in the length of the key which can be 40,64 or 128 bits and in the number of rounds, typically ranging between 5 and 10.

We have designed the first VLSI circuit for the SAFER family. Thej versatile microchip enchipers and deciphers according to the SK-40, SK-64 and SK-128 algorithms. Separate ports are provided for ciphertext, plaintext and control. The requirement of supporting all four of the standard cipher operating modes (ECB, CBC, CFB, OFB) proved rather onerous in terms of silicon area. The cell based full-custom IC has been designed using a 1.2um CMOS technology and with the aid of VHDL synthesis software. Die size is 40sqmm, samples are encapsulated in a PGA84 package. Throughput depends on the number of rounds. Processing of one round takes 9 clock cycles, and simulations indicate a mximum clock frequency in excess of 20 MHz.

There are some funny messages on the chip: