The IIS Chip Gallery

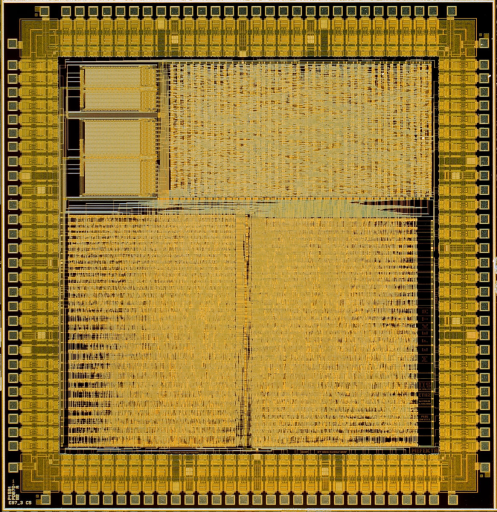

Mefekta (1996)

by

| Application | Processor |

| Technology | 800 |

| Manufacturer | ES2 |

| Type | Research Project |

| Package | PGA120 |

| Dimensions | 5400μm x 5500μm |

| Voltage | 5 V |

| Power | 540 mW |

| Clock | 50 MHz |

An application-specific microprocessor core with stack architecture has been developed. It is optimized for use in an Add-Drop-Multiplexer for the Synchronous Digital Hierarchy (SDH).

The processor is able to handle in excess of one Million interrupts per second from 29 asynchronous sources. This high interrupt rate requires extremely efficient context switching: not more than two extra cycles per interrupt call. The top four stack elements are directly accessable as registers, ALU instructions are computed in parallel with push or pop commands, and an independent ALU processes addresses.

The embedded stack processor features a three stage pipeline: instruction fetch, instruction decode and execute and write back. Delayed branch execution prevents pipeline stalls. Data width is 8 bits while instructions use 16 bits. The memory is organized as separate data and program sections (Harvard architecture).