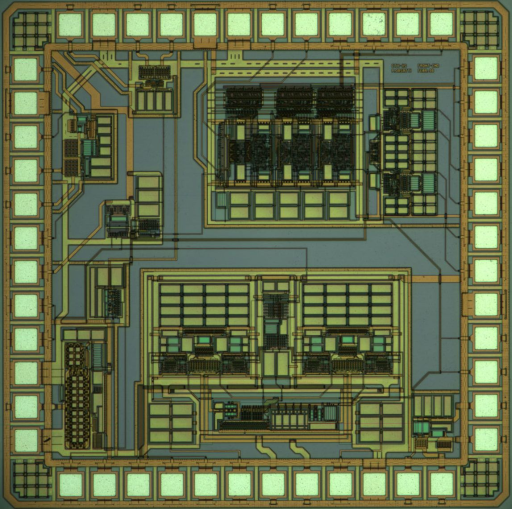

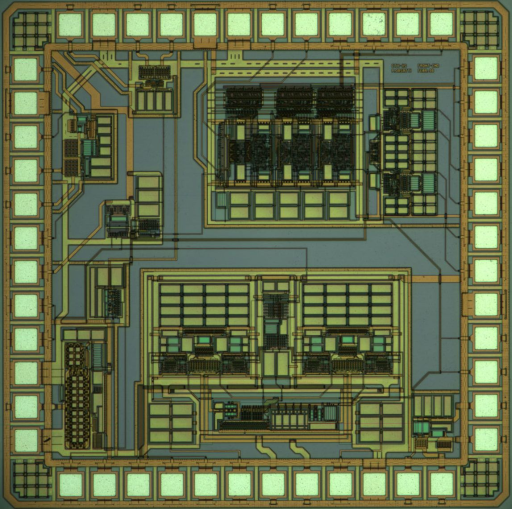

The IIS Chip Gallery

GSM (1998)

by

| Application | Communication |

| Technology | 250 |

| Manufacturer | Toshiba |

| Type | Research |

| Package | LCC48 |

| Voltage | 2.5 V |

| Power | 50 mW |

In a typical GSM handset the battery takes up as much as 20% of the cost, as well as volume and weight. Power consumption, which dictates the required battery, is therefore the most important consideration in the design of transceiver ICs, once the necessary performance requirements for type approval are met.

In this project a complete single-chip GSM transceiver in a low cost 0.25um CMOS technology has been realized and characterized. The transmitter section uses a direct-conversion architecture. It includes the I,Q modulator with integrated phase shifter and a preamplifier. The transmitter can deliver the required 2 mWto an external power amplifier keeping the distortion level well below the maximum allowed by specifications. The receiver has been implemented using a single-superheterodyne architecture with 71 MHz intermediate frequency. The integrated part contains the RF front-end with LNA and mixer and the complete IF-baseband-strip. Thanks to the careful design, optimized for low power consumption, the receiver meets all GSM requirements while consuming only 50 mW. It is worth to note that this power level, which is about 40% less than the one needed by current commercial bipolar implementations, is the lowest reported to date for any technology.