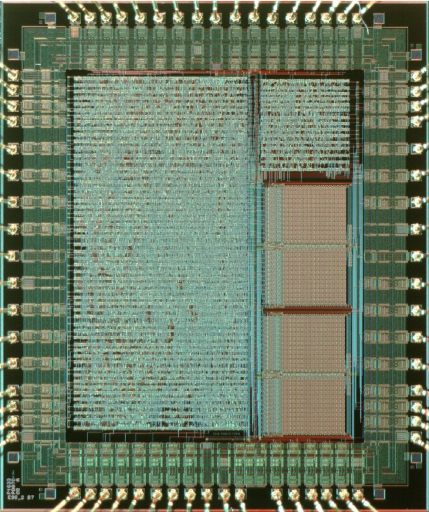

The IIS Chip Gallery

Tester (1998)

by

State-of-the-art equipment for manufacturing testing of ICs are sophisticated machines of substantial costs. The aim of this semester thesis was to develop a solution for the student testing lab, providing the basic functionality of industrial testers at a considerable lower expense.

The ASIC tester has been designed as one-chip test system with minimum additional hardware requirements. The tester chip is responsible for stimulus data application to and response acquisition from the device under test (DUT). Test operation can be controlled from a standard computer which is connected via a bidirectional parallel interface to the tester chip. A specialized instruction set is used to control the configuration of the tester chip.

Each of the DUT pins can be configured as input, output or bidirectional port. Four different waveforms including Return to Zero/One, Delayed Non Return to Zero and Delayed Return to High Impedance may be selected individually for input ports. The acquisition time is programmable per output port, alleviating timing related testing. A small on-chip memory for stimuli and response data accommodates limited speed testing. For DUTs with high pin count several tester chips can work in parallel without additional handshake lines to the computer.