The IIS Chip Gallery

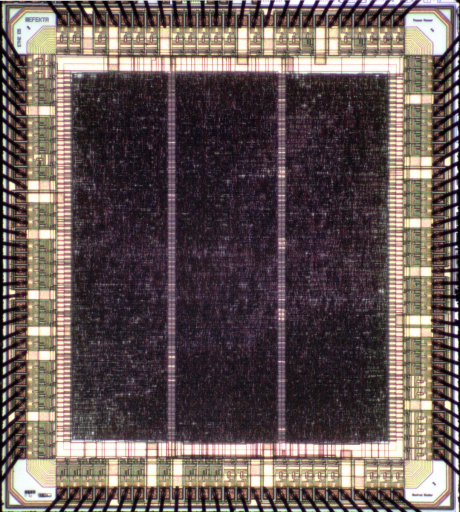

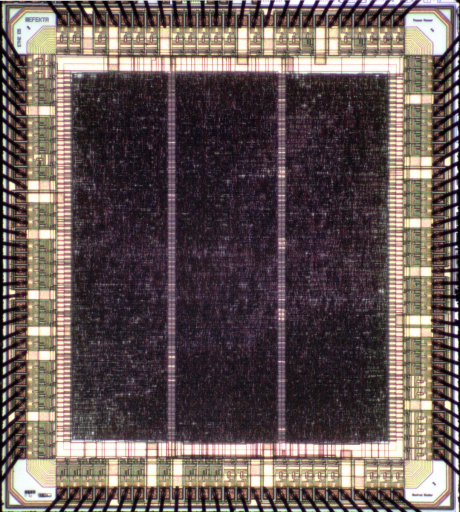

Mefekta2 (1999)

by

| Application | Processor |

| Technology | 600 |

| Manufacturer | austriamicrosystems |

| Type | Research |

| Dimensions | 4500μm x 4100μm |

| Gates | 0 |

| Voltage | 5 V |

| Clock | 111 MHz |

Customizable microprocessors pose numerous design problems that arise from application-specific needs for data operations, word widths, storage capacities, and interfaces. A stack processor that features a customizable instruction set, extensive parameterization, and a synthesis model with separate core and interface modules has been designed in this work. It can be tuned to the application-specific needs of the user by means of 100 parameters.

Application- or customer-specific scalability and programmability, however, introduce severe difficulties into the functional verification flow. For this IP a two-step functional verification flow has been developed. In the first step a configuration-independent behavioral model is applied to generate the test pattern using assembler code as stimuli. In the second simulation run the expected responses, generated by the behavioral model, are compared against the output of the parameterized RTL model of the IP module, and a report is generated.