The IIS Chip Gallery

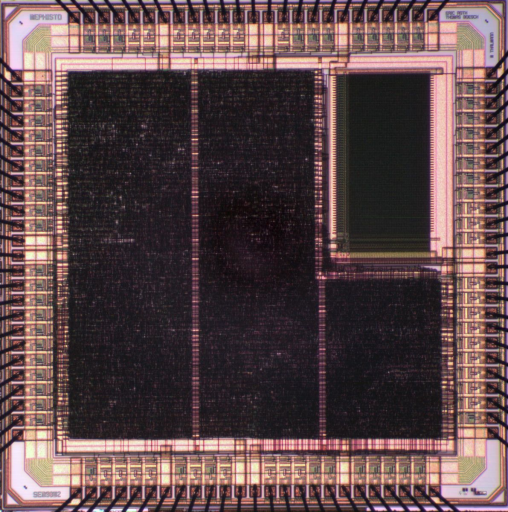

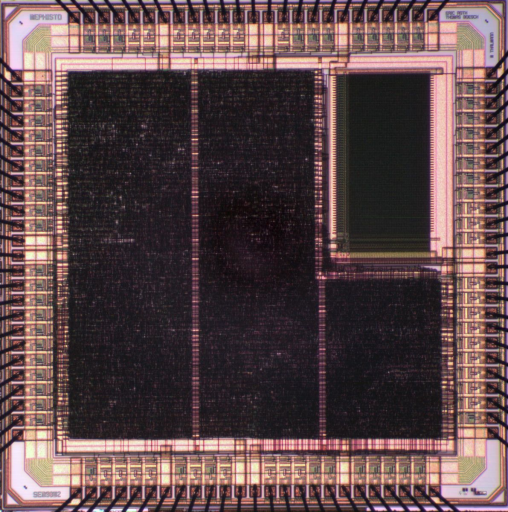

Mephisto (1999)

by

| Application | Processor |

| Technology | 600 |

| Manufacturer | austriamicrosystems |

| Type | Semester Thesis |

| Package | PGA100 |

| Voltage | 3.3 V |

This processor core called MEPHISTO has been developed in a student thesis. It is optimized to extend handheld GPS receivers by additional functions. The Application Specific Instruction set Processor (ASIP) features many GPS-specific one-clock-cycle instructions such as multiply-accumulate, cosine-lookup, division by ten, and chainable arithmetic operations. For fast response and easy data transfer the ASIP is optimized to handle a very high interrupt rate. The stack architecture with several directly accessible top-of-stack registers enables ultra-fast context switching without affecting performance. Special instruction versions make efficient use of registers. Delayed branch and a Harvard RAM architecture enable efficient code processing. Dense 14 bit code and powerful instructions reduce the program RAM requirements.