The IIS Chip Gallery

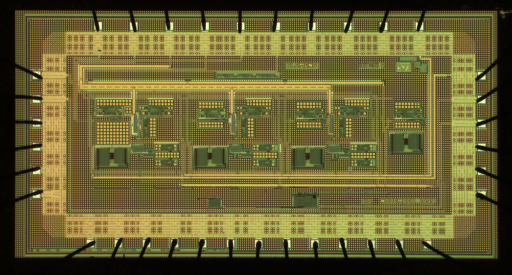

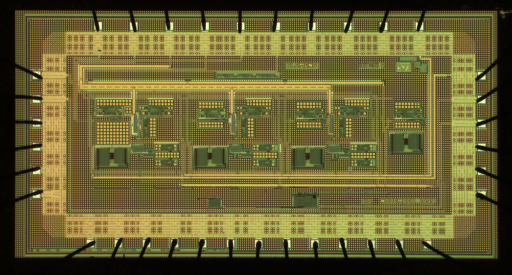

PipelinedAD (1999)

by

| Application | Converter |

| Technology | 250 |

| Manufacturer | STM |

| Type | Research |

| Dimensions | 4364μm x 2207μm |

| Voltage | 2.5 V |

| Power | 117.5 mW 2.5V |

New wire-line communication systems such as ADSL (Asymmetric Digital Subscriber Line) or VDSL (Very High Speed Digital Subscriber Line) that provide highspeed internet access via standard telephone lines require A/D converters with resolutions of 12 to 13 bit and conversion rates of several Msample/s. Moreover, the A/D converters should be integrated in a standard digital deep submicron CMOS process such that the analog front-end and the digital signal processing circuitry can be co-integrated on the same chip.

The A/D converter developed in this project utilizes a pipeline architecture with four stages. The D/A converter, which is the most important building block of a pipeline stage in terms of linearity, consists of a MOSFET-only R-2R ladder. This type of ladder has shown excellent matching performance in previous applications. Due to the exclusive use of MOS transistors, this circuit can be implemented in every standard digital CMOS process without the need of special passive devices.

The A/D converter is implemented in a 0.25um CMOS process with a supply voltage of 2.5 V. Its resolution is 13 bits with a conversion speed of 5 Msample/s. The measured total harmonic distortion (THD) at full speed is -70 dB. The power consumption is moderate 118 mW