The IIS Chip Gallery

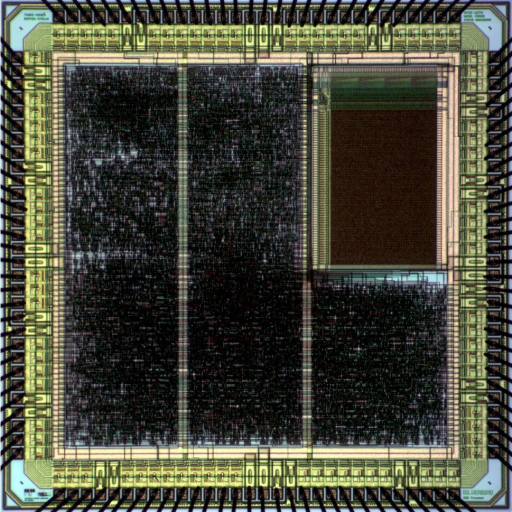

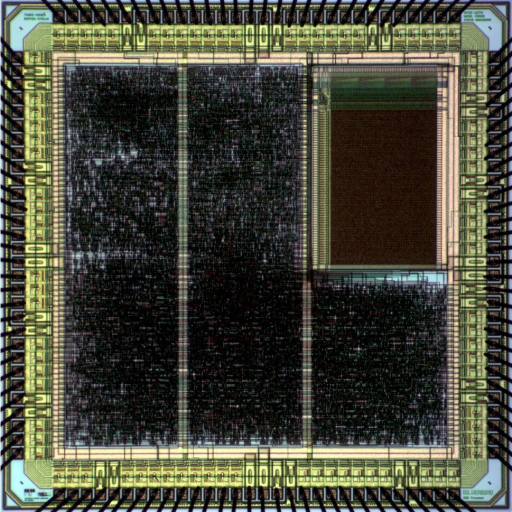

Silverbird (2000)

by

| Application | Processor |

| Technology | 600 |

| Manufacturer | austriamicrosystems |

| Type | Semester Thesis |

| Package | PGA120 |

| Dimensions | 4600μm x 4600μm |

| Gates | 25 kGE |

| Voltage | 5 V |

| Clock | 118.6 MHz |

The result of this semester thesis is an IP module or a virtual component (VC) of a RISC processor core. It realizes a Harvard architecture with a four-stage pipeline and delayed branch instructions. The register bank of the processor is implemented as top-ofstack which results in very efficient interrupt handling capability.

The source of the processor in hardware-description language (VHDL) enables the designer, who wants to use this VC, to parametrize it in stack and memory width as well as in the RISC instruction set. The less instructions are selected, the lower the amount of silicon will be after synthesis.

The virtual component has been integrated to verify the concept. Key specifications and parameter set of the student chip called SILVERBIRD are: