The IIS Chip Gallery

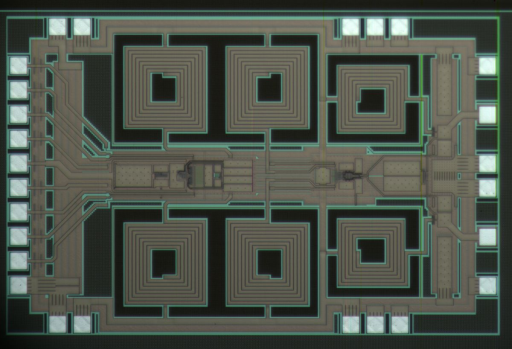

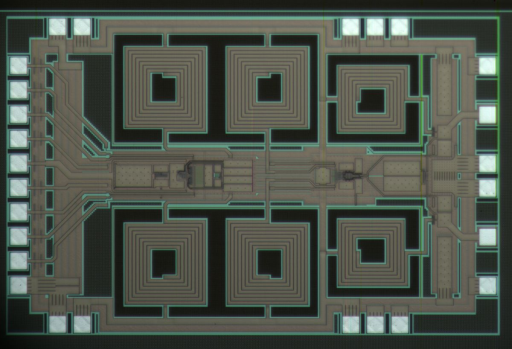

QuadDemod (2001)

by

| Application | Communication |

| Technology | 180 |

| Manufacturer | TSMC |

| Type | Research |

| Package | Baredie |

| Dimensions | 2300μm x 1500μm |

| Voltage | 1.8 V |

| Power | 18 mW, 1.8V |

Low IF- and zero-IF receivers are attractive architectures for highly integrated receivers. However, the required quadrature demodulator at RF tends to increase the power consumption ofsuch receivers substantially. Innovative design techniques must be used to compete with low power superheterodyne receivers.

A quadrature demodulator consisting ofa 3.6 GHz oscillator, quadrature divider and down-conversion mixers has been implemented. Among other power saving techniques, the low phase-noise oscillator's consumption could be kept low at only 3mA because a high-Q radial stripline resonator was used instead ofspir al inductors. The stripline is integrated into inner layers ofthe printed circuit board to keep the board size small.

Good measured performance on all building blocks (e.g 40 dB image rejection, 8.5 dBm mixer IP3, -3 dBm mixer compression point) was observed despite the extremely low overall consumption of 10 mA. The circuits are implemented in standard 0.18 um CMOS.