The IIS Chip Gallery

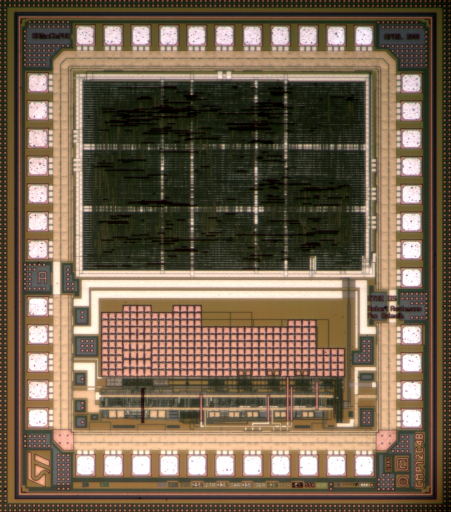

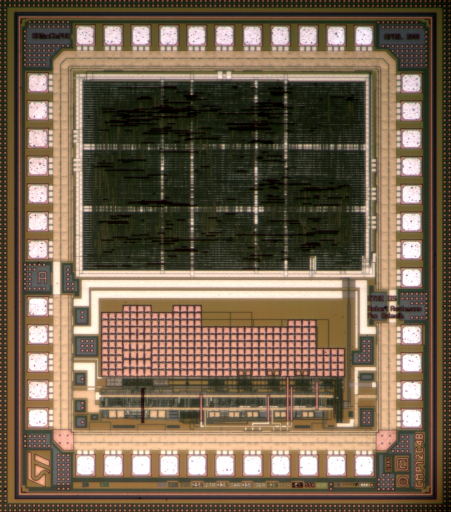

SDmixChipV2 (2001)

by

| Application | Converter |

| Technology | 250 |

| Manufacturer | STM |

| Type | Research Project |

| Dimensions | 1600μm x 1500μm |

| Voltage | 1.2-2.5 V |

| Power | 33 mW |

In both wired and wireless communications applications, such as DSL, PLC or DECT, low power consumption is highly desirable. Recent publications show that for 1-2 MHz signal bandwidth, sufficient resolution (more than 13b) for typical communications requirements can be achieved by over-sampled converters. Typical power consumption, however, is above 150 mW for a SD modulator alone and 190mW with the necessary digital filtering.

In this project, a low-power SD A/D converter has been implemented in a 0.25 um digital CMOS process. The IC consists ofa 5th order SD modulator with a tri-level quantizer and a multi-stage digital decimation filter. With an input sampling rate of 80 MHz and an oversampling ratio of 32, a peak SNR of 84 dB and a peak SNDR of 79 dB have been measured at the 2.5 MS/s filtered digital output. The signal bandwidth of the converter is 1 MHz.

The modulator is implemented using a fully differential switched capacitor circuit style. It occupies a core area of 0.6 mm2 and consumes 24 mW from a 2.5 V supply. The digital filter, consisting of one comb stage and two FIR stages, uses a core area of 0.9 mm2 and has a power consumption of 9 mW, using a core supply voltage of 1.25 V.

The complete mixed signal IC has a core area of 1.5 mm2 and a total die area of 2.5 mm2. The total 14-bit, 2.5 MS/s A/D converter consumes only 33 mW, which is significantly lower than the power consumption reported for comparable previous SD converters or modulators.