The IIS Chip Gallery

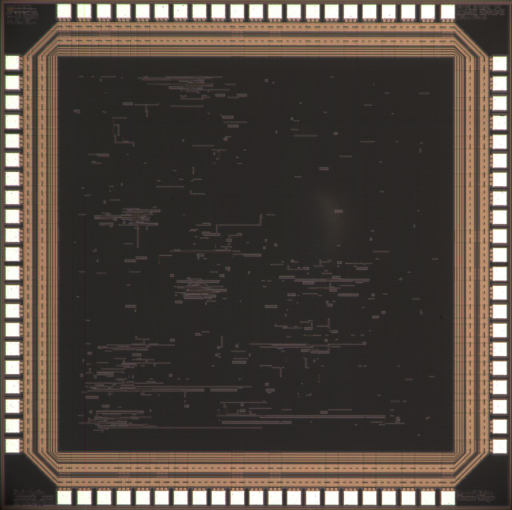

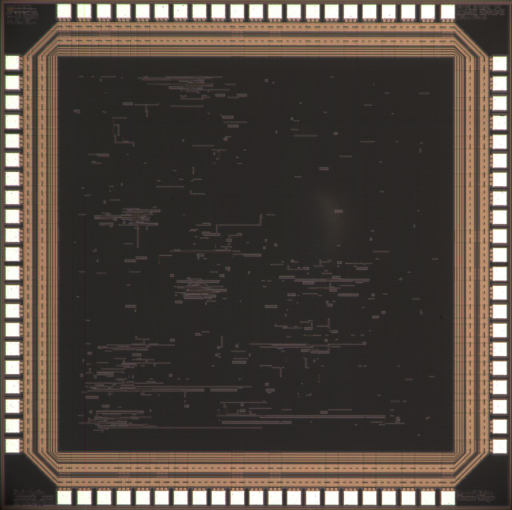

AudioMixer (2003)

by

| Application | Audio |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 2.5 V |

| Clock | 24.576 MHz |

With several of these ASICs designed by a group of two computer science and one electrical engineering students a digital audio mixing console can be realized. Each of the chips accepts four digitized stereo channel pairs in the industry standard I2S format. Before the weighted addition, commonly referred to as mixing, the stereo signals can be individually amplified and filtered by increasing or decreasing the bass, middle, or treble frequency ranges, i.e. below, between, and above 300Hz and 4000 Hz. The filters are of order two, four, and two. The selectable gain range is from -20dB to +20dB in 2dB steps.

The following mixing section allows to add the channels with selectable weight factors between 24dB gain and 108dB attenuation in 0.5dB steps, and mute. A switchable soft-clip circuit limits unintended overdrive in a less hearable way. LEDs can be connected to warn the user when clipping occurs. Before passing the signals to the I2S outputs, a master volume control with the same range as the weight factors is inserted.

The mixer chip runs with a 24.576MHz clock and works at the audio sample rate of 96 kHz with 24bit precision. The chip has been fabricated at UMC in 0.25um CMOS technology and afterwards verified functionally and through its full-scan path with a stuck-at fault coverage of 95%. All 10 packaged prototypes showed full functionality.