The IIS Chip Gallery

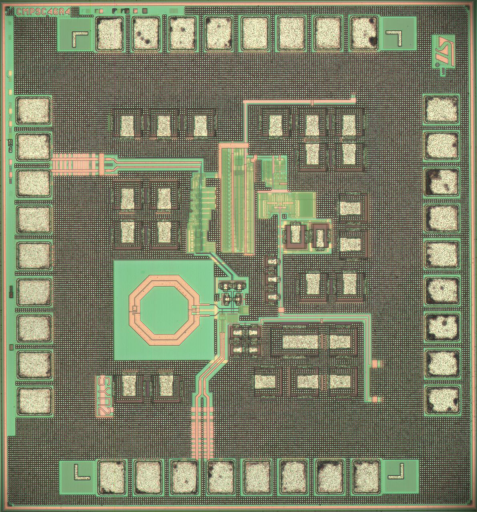

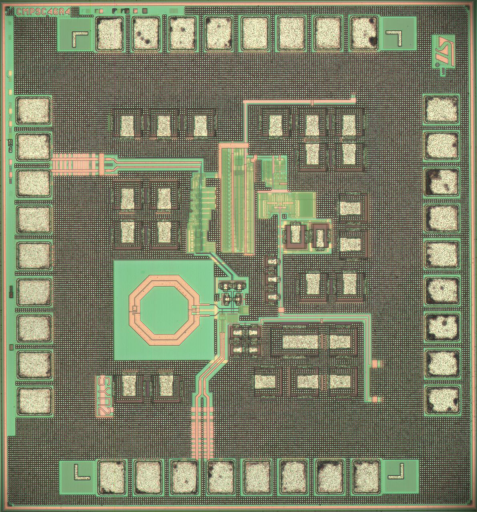

SYN2 (2004)

by

| Application | Communication |

| Technology | 130 |

| Manufacturer | STM |

| Type | Research |

| Package | LCC44 |

| Voltage | 1.2 V |

| Power | 9.5 mW |

Third-generation cellular radio networks based on Wide-band Code Division Multiple Access (WCDMA) are growing rapidly and are believed to dominate the market in the near future. Given the substantial amount of digital signal processing, fine line CMOS technologies with gate lenghs of 0.13 um or even below are preferred to realize low power, cost effective solutions. A RF front-end in the same technology simplifies the technology mix for the wireless chip set and offers a potential for higher integration level.

In contrast to GSM, where in TDMA mode of operation a lower duty cycle helps curtail power consumption, the FDD of the WCDMA standard requires both the receiver and transmitter to operate continuously. Power consumption is therefore one of the limiting factors in the potential success of 3G cellular services and low power design has never been more important for the RF transceiver.

In this project, a 4 GHz single-band WCDMA frequency synthesizer, including an on-chip VCO, has been realized in standard 0.13 um CMOS technology. It is based on integer-N architecture in order to save die area as well as power consumption. With careful circuit design, reference spurs that tend to be problematic in integer-N synthesizers have been reduced to appropriate levels. The overall performance meets UMTS specifications with a low power consumption of merely 9.5 mW, which is the lowest reported to date. Core area of the chip is as small as 0.2 mm2, which is a favorable attribute for a single-chip UMTS transceiver.