The IIS Chip Gallery

Cite (2005)

by

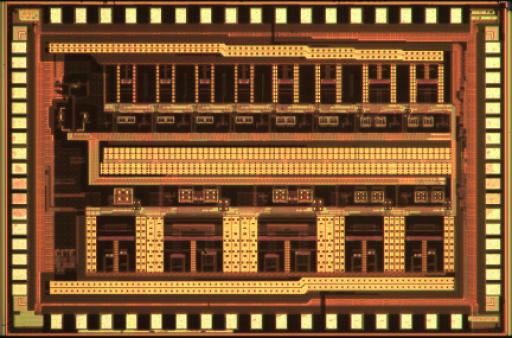

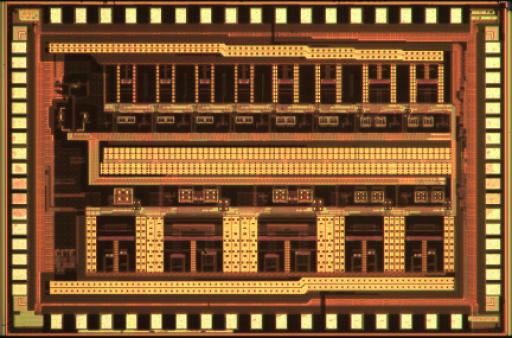

| Application | Converter |

| Technology | 130 |

| Manufacturer | STM |

| Type | Research Project |

| Package | LCC68 |

| Dimensions | 2655 μm x 1743 μm |

| Gates | 0 |

| Voltage | 1.2 V |

| Power | 122 mW |

| Clock | 50 MHz |

Recent developments in wireless and wirebound communication systems have created a growing demand for analog-todigital converters (ADCs) featuring medium resolution combined with high throughput. These ADCs must be producible in mainstream deep-submicron technologies together with digital circuitry, for example digital signal processors (DSPs), as systems-on-a-chip.

Pipelined ADCs have the potential to fulfill the aforementioned demands. Recent publications underline the growng capabilities of the pipelined architecture, as there are designs available with excellent spurious free dynamic range (SFDR) characteristics combined with sampling rates significantly above 20 MS/s.

A major limit to the performance of pipelined ADCs is the mismatch among different components with nominally eqal sizes, which is intrinsic to every manufacturing process.

In this work, a double sampling and averaging scheme to counter component mismatch has been implemented in a 1.5-bit pipelined ADC composed of differently scaled 1.5-bit stages.

After digital correction, the manufactured chip is able to reach more than 10 effective bits (ENOB) over a bandidth of 25 MHz at a supply voltage of 1.2 V while consuming 122 mW of power.