The IIS Chip Gallery

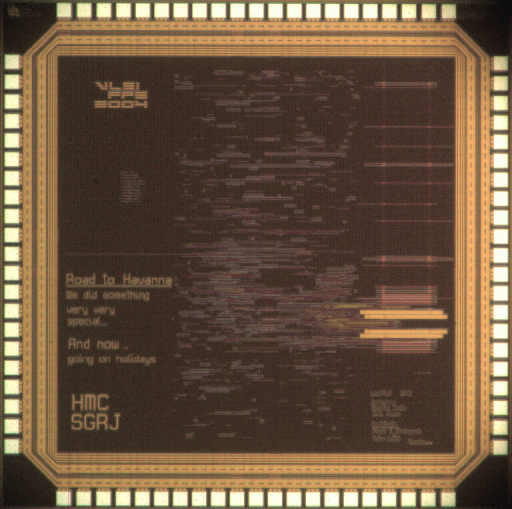

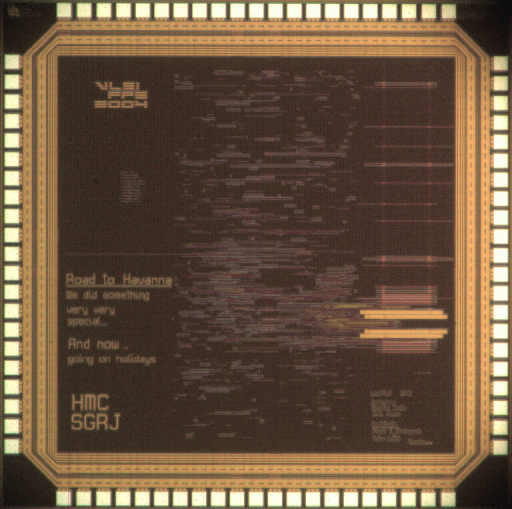

HavannaClub (2005)

by

| Application | Test |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Gates | 80 kGE |

| Voltage | 2.5 V |

| Clock | 80 MHz |

The production of integrated circuits (IC) is a very complex process which is hard to control. A small percentage of manufactured ICs will therefore contain errors that will prevent the IC from functioning correctly. Production tests ensure that these faulty ICs are sorted out. These chips are said to contain hard-errors since the chip will always exhibit faulty behavior.

It is also possible to induce hard-errors during operation, for example by applying input voltages above the maximum allowable range. Similar to hard-errors during manufacturing, these errors will cause the IC to malfunction permanently.

Soft-errors, on the other hand, are defined as errors that induce faulty behavior only for a limited time. These can be induced through operating conditions, radiation, or noise. Soft-errors can only be reliably detected if the IC is continuously checked during operation.

In this project, a simple ALU was implemented using different concurrent error detection algorithms. To prove the efficiency of the algorithms, the netlist of the design has been artificially altered to induce up to 256 separate stuck-at fault errors. In this way, soft-errors can be introduced during operation, for the evaluation of the efficiency of the error detection.

On the top left corner of this chip, there is a small block which is not connected to the padframe. This block contains the small full custom viterbi decoder that was made during the PPS-VLSI of 2004. Curiously this is not the original layout by the students, since that was made using ST 0.25um technology which is not compatible to the UMC process. The layout was completely redrawn for UMC sticking as close as possible to the original layout.