The IIS Chip Gallery

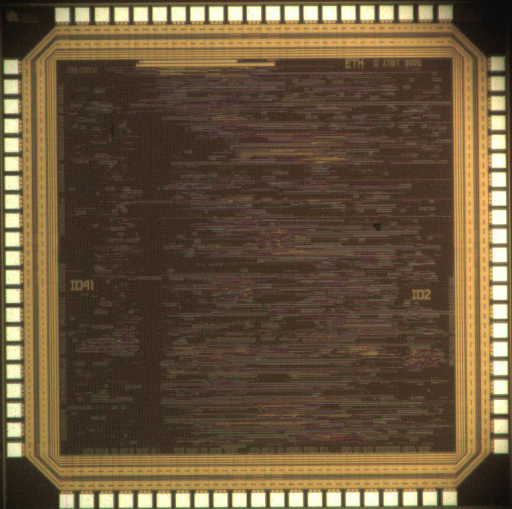

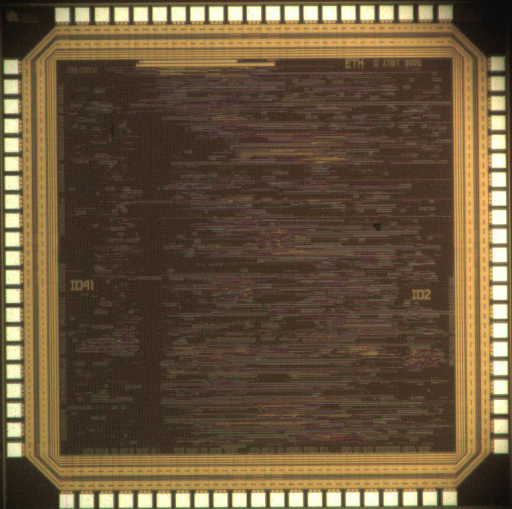

Hearing_Aid (2005)

by

| Application | Low-power |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 2.5 V |

| Power | 0.742 mW, 2MHz, 2.5V |

| Clock | 105.2 MHz |

The aim of this semester project was the analysis of the power-area trade-off in functionally equivalent implementations of a speech enhancement algorithm.

Hearing-impaired people often suffer from a reduced intelligibility of speech in noisy environments. Based on adaptive filtering, the algorithm identifies the so-called formants, which are the most important frequency contributions for speech comprehensibility, and accentuates them. The filter has been implemented by means of a lattice structure. It has been assembled with identical stages, one per filter order, which is 8 in this case. The stages are lined up sequentially, which permits the implementation of the algorithm by different levels of iterative decomposition by reusing the stages (resource sharing). For this project, a 2nd level architecture (ID2) has been integrated on silicon. This means that each sample is looped twice through four stages. Additionally, a fully decomposed architecture (ID41), using only one adder, multiplier and barrel shifter, has been integrated. Design ID2 dissipates 0.65 mW (7.72 mm2), whereas ID41 consumes 1.4 mW (0.78 mm2).

Furthermore, simulations have shown that the most energy efficient architecture would be located between the two extremes. This design (ID8) does not break up the structure of the lattice stages, and hence does not suffer from extensive glitch propagation, as is the case in ID2.