The IIS Chip Gallery

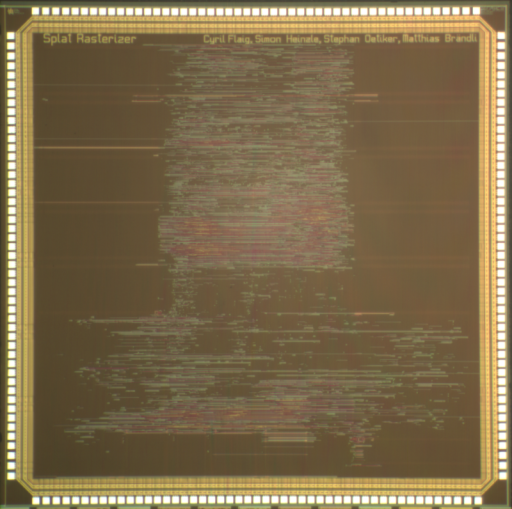

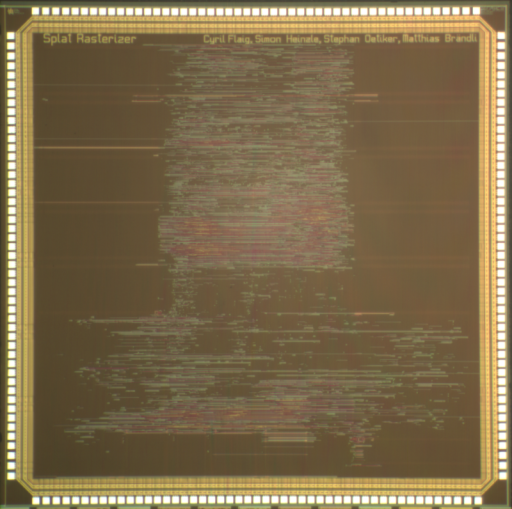

Splat (2005)

by

| Application | Graphics |

| Technology | 250 |

| Manufacturer | UMC |

| Type | Semester Thesis |

| Package | PGA208 |

| Dimensions | 5000μm x 5000μm |

| Gates | 800 kGE |

| Voltage | 2.5 V |

| Clock | 196 MHz |

This ASIC was developed in collaboration with the Computer Graphics Laboratory of ETHZ (CGL). Point based rendering has experienced a renaissance over the past few years. It offers some advantages over traditional triangle and polygon based rendering methods when it comes to smooth curved surfaces, and does away with the limitations of triangle meshes and their connectivity overhead. On the other hand, point-based rendering requires high resolution models and therefore, demands high computational effort and memory bandwidth. In spite of all this research, hardware implementations of this alternative rendering approach were still missing. For this ASIC concentration was put on the EWA splatting approach for point based rendering. The proposed architecture produces high quality images at interactive frame rates and with high resolution. The huge bandwidth requirements in order to access the external frame buffer were solved with an intelligent on-chip caching strategy and an on-chip heap.

The ASIC's main operating frequency is 200 MHz. An input FIFO buffer allows asynchronous delivery of the data to be rasterized. After an image is rendered, the data is output over a 8 bit parallel bus to a USB 2 transmitter chip. An on-chip sigma-delta oscillator allows the user to program the output frequency of this bus up to 100 MHz.

The EWA Splat Rasterizer was fabricated on a 0.25um five-metal-layer CMOS process by UMC and has a total die area of 25mm2. The 208 Pin-Grid-Array package is a trade-off between pin count and the high bandwidth requirements of the external frame buffer.