The IIS Chip Gallery

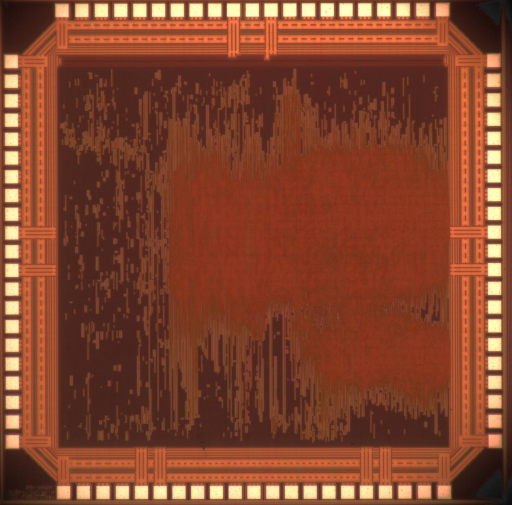

Hearingaid (2006)

by

| Application | Low-power |

| Technology | 180 |

| Manufacturer | UMC |

| Type | Research Project |

| Package | LCC84 |

| Dimensions | 2500μm x 2500μm |

| Voltage | 0.75 V |

| Power | 0.100 mW |

Two versions of a front-end for digital hearing aids have been placed on the same die and fabricated in a 0.18 mm CMOS technology (VDD = 0.75 V). The difference is in the set of standardcells made available to the synthesis tool. In the reference design, a regular industrial cell library has been used, while a few hand-crafted cells featuring transistors of minimum size have been added for the second design. Measurements on real silicon show that the second version with about one quarter of all cells replaced by minimum- drive variants saves about 29 % of energy, compared to the reference. The approach has the benefit of being fully compatible with current design and fabrication flows. An open point in this work is the selection of the cells to be re-designed in order to obtain the most power-efficient solution with reasonable design effort.

The implemented front-end contains two different typical hearing aid algorithms that are usually applied one after the other. The first one, a so-called directional microphone, separates speech from noise by exploiting their spatial diversity. Thereby, it is assumed that the speech arrives from the front, while the disturbing noise comes from the back.

The output signal of the directional microphone is then fed to the second algorithm performing noise reduction. It separates the signal into subbands. The bands which show a more or less constant power are assumed to contain noise and are hence attenuated accordingly.